#### **ELASTICITY AND PETRI NETS**

Jordi Cortadella, Universitat Politecnica de Catalunya, Barcelona Mike Kishinevsky, Intel Corp., Strategic CAD Labs, Hillsboro

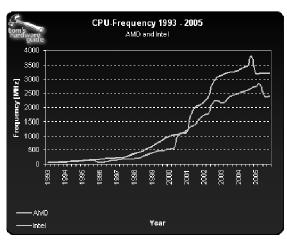

#### Is the GHz race over ?

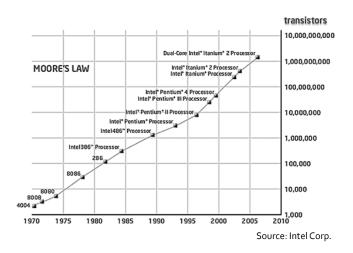

#### Moore's law

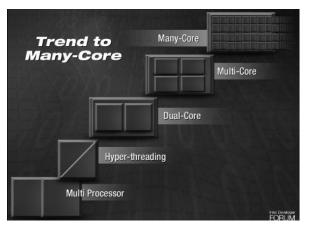

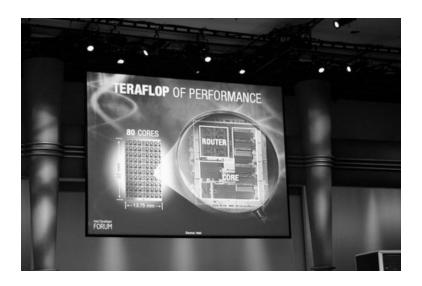

## Many-Core is here

Source: Intel Corp.

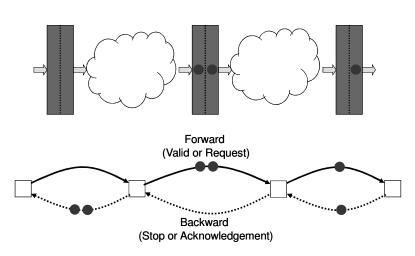

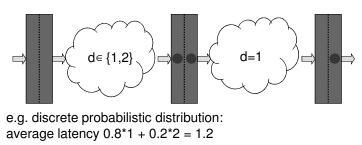

Elasticity

- Tolerance to delay variability

- Different forms of elasticity

- Asynchronous: no clock

- $\ ^{\square}$  Synchronous: variability synchronized with a clock

- In all forms of elasticity, token-based computations are performed (req/ack, valid/stop signals are used)

#### Why this tutorial ?

- Digital circuits are complex concurrent systems

- Variability and power consumption are key critical aspects in deep submicron technologies

- Multi (many)-core systems will become a novel paradigm:

- System design

- Applications

- Concurrent programming

- Theory of concurrency may play a relevant role in this new scenario

#### Outline

- Asynchronous elastic systems

- The basics: circuits and elasticity

- $\, {}^{\scriptscriptstyle \perp} \,$  Synthesis of asynchronous circuits from Petri nets

- Modern methods for the synthesis of large controllers

- De-synchronization: from synchronous to asynchronous

- Synchronous elastic systems

- Basics of synchronous elastic systems

- Early evaluation and performance analysis

- Optimization of elastic systems and their correctness

## THE BASICS: CIRCUITS AND ELASTICITY

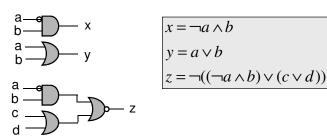

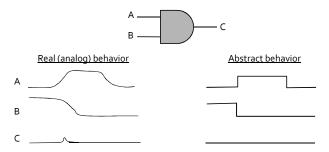

#### Boolean functions

Composed from logic gates

#### Outline

- Gates, latches and flip-flops.

Combinational and sequential circuits.

- Basic concepts on asynchronous circuit design.

- Petri net models for asynchronous controllers. Signal Transition Graphs.

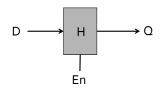

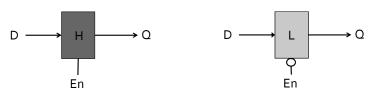

#### Memory elements: latches

#### Active high:

En = o (opaque): Q = prev(Q)

En = 1 (transparent): Q = D

#### Active low:

En = 1 (opaque): Q = prev(Q)

En = o (transparent): Q = D

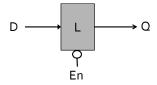

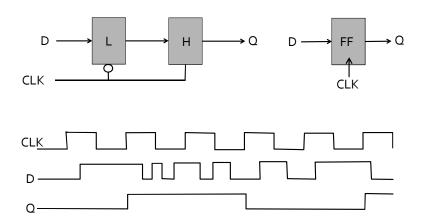

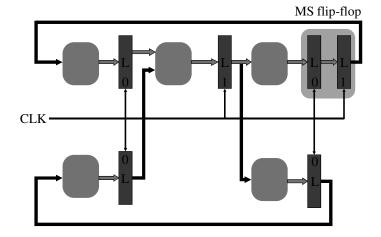

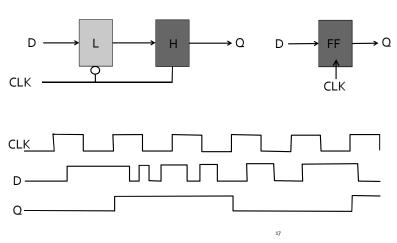

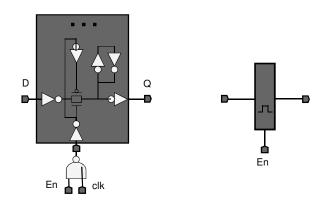

## Memory elements: flip-flop

#### Finite-state automata

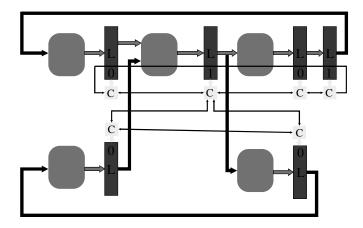

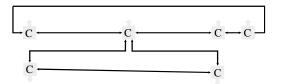

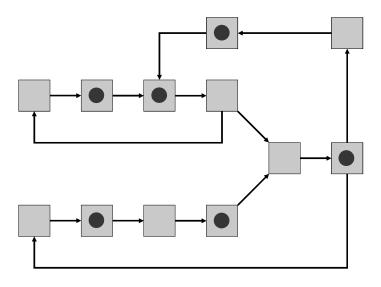

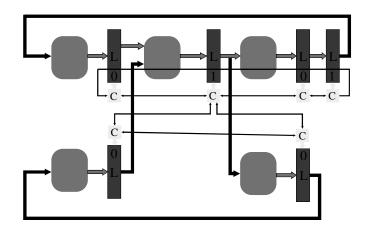

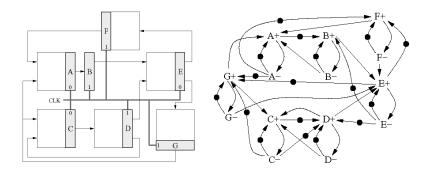

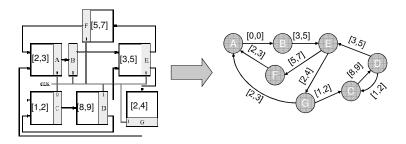

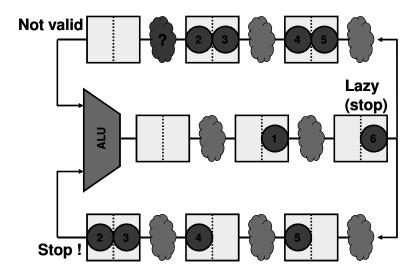

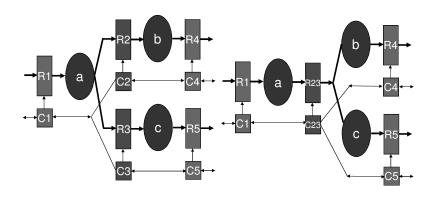

## Network of Computing Units

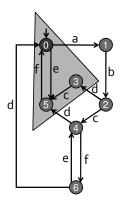

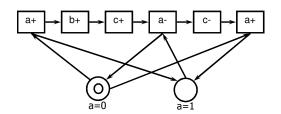

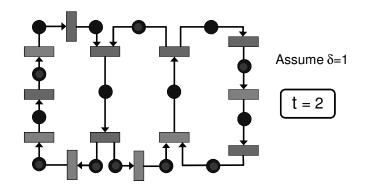

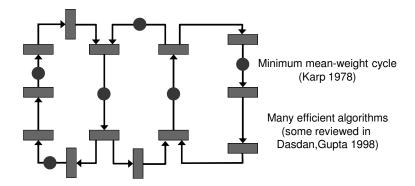

## Marked Graph Model

# BASIC CONCEPTS ON ASYNCHRONOUS CIRCUIT DESIGN

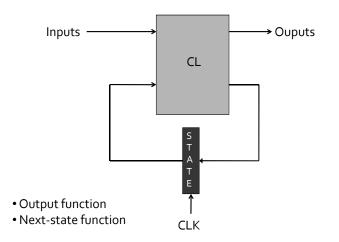

Synchronous circuit

Implicit (global) synchronization between blocks Clock period > Max Delay (CL + R)

#### Outline

- What is an asynchronous circuit?

- Asynchronous communication

- Asynchronous design styles (Micropipelines)

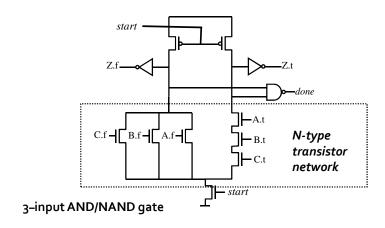

- Asynchronous logic building blocks

- Control specification and implementation

- Delay models and classes of async circuits

- Channel-based design

- Why asynchronous circuits?

#### Asynchronous circuit

Explicit (local) synchronization: Req / Ack handshakes

#### Motivation for asynchronous

- Asynchronous design is often unavoidable:

- Asynchronous interfaces, arbiters etc.

- Modern clocking is multi–phase and distributed and virtually 'asynchronous' (cf. GALS – next slide):

- Mesachronous (clock travels together with data)

- Local (possibly stretchable) clock generation

- Robust asynchronous design flow is coming (e.g. VLSI programming from Philips, Balsa from Univ. of Manchester, NCL from Theseus Logic ...)

#### **Key Design Differences**

- Synchronous logic design:

- proceeds without taking timing correctness (hazards, signal ack-ing etc.) into account

- Combinational logic and memory latches (registers) are built separately

- Static timing analysis of CL is sufficient to determine the Max Delay (clock period)

- Fixed set–up and hold conditions for latches

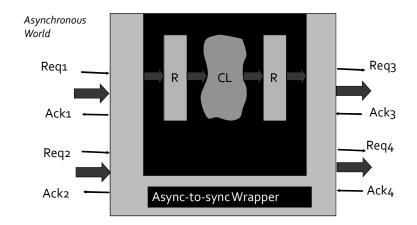

#### Globally Async Locally Sync (GALS)

#### **Key Design Differences**

- Asynchronous logic design:

- Must ensure hazard–freedom, signal ack–ing, local timing constraints

- Combinational logic and memory latches (registers) are often mixed in "complex gates"

- Dynamic timing analysis of logic is needed to determine relative delays between paths

- To avoid complex issues, circuits may be built as Delay-insensitive and/or Speed-independent (as discussed later)

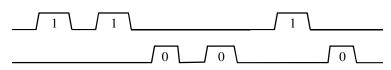

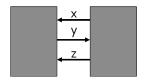

#### **Synchronous communication**

- Clock edges determine the time instants where data must be sampled

- Data wires may glitch between clock edges (set-up/hold times must be satisfied)

- Data are transmitted at a fixed rate (clock frequency)

#### Bundled data

- Validity signal

- Similar to an aperiodic local clock

- *n*-bit data communication requires *n*+1 wires

- Data wires may glitch when no valid

- Signaling protocols

- level sensitive (latch)

- transition sensitive (register): 2-phase / 4-phase

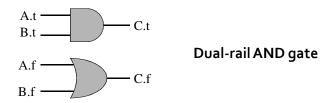

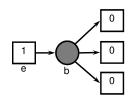

#### Dual rail

- Two wires with L(low) and H (high) per bit"LL" = "spacer", "LH" = "o", "HL" = "1"

- *n*−bit data communication requires 2*n* wires

- Each bit is *self-timed*

- Other delay-insensitive codes exist (e.g. k-of-n) and event-based signalling (choice criteria: pin and power efficiency)

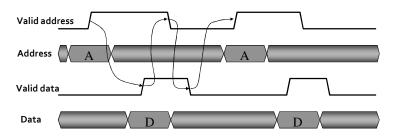

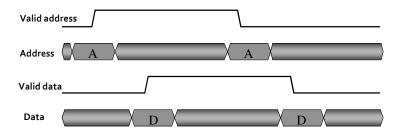

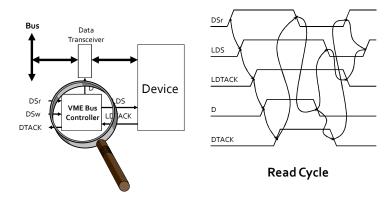

#### Example: memory read cycle

Transition signaling, 4-phase

#### Example: memory read cycle

Transition signaling, 2-phase

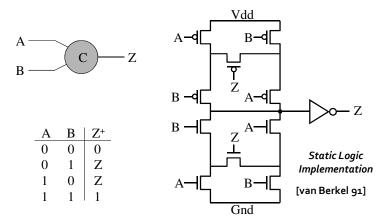

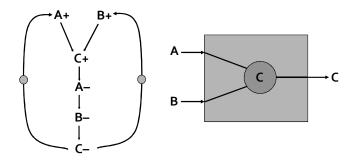

#### Asynchronous latches: C element

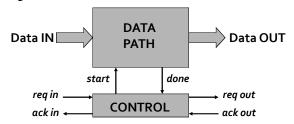

#### Asynchronous modules

#### Signaling protocol:

reqin+ start+ [computation] done+ reqout+ ackout+ ackin+ reqin- start- [reset] done- reqout- ackout- ackin- (more concurrency is also possible)

#### C-element: Other implementations

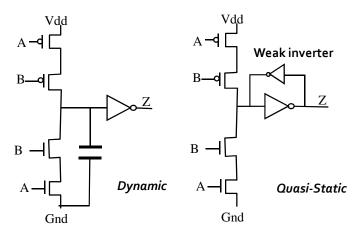

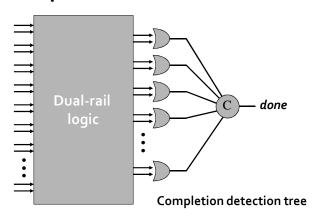

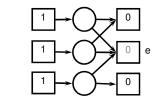

#### Dual-rail logic

Valid behavior for monotonic environment

#### Differential cascode voltage switch logic

#### **Completion detection**

#### Example of dual-rail design

- Asynchronous dual-rail ripple-carry adder (A. Martin, 1991)

- Critical delay is proportional to logN (N=number of bits)

- 32-bit adder delay (1.6m MOSIS CMOS): 11 ns versus 40 ns for synchronous

- Async cell transistor count = 34

versus synchronous = 28

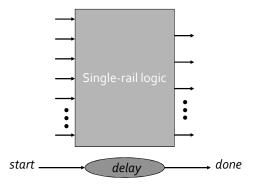

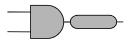

## Bundled-data logic blocks

Conventional logic + matched delay

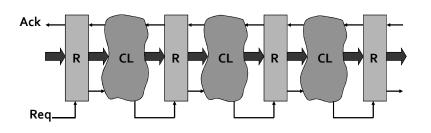

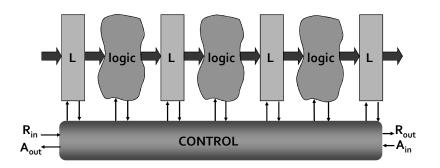

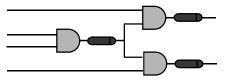

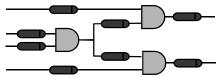

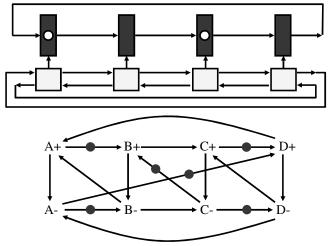

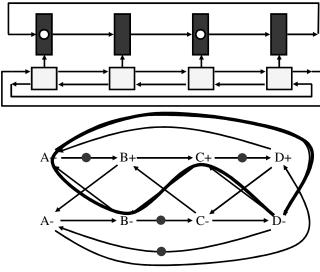

## Micropipelines (Sutherland 89)

Micropipeline (2-phase) control blocks

## Micropipelines (Sutherland 89)

#### Data-path / Control

## Control specification

## Control specification

## **Control specification**

## **Control specification**

#### **Control specification**

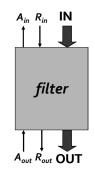

## A simple filter: specification

```

y:= o;

loop

x:= READ (IN);

WRITE (OUT, (x+y)/2);

y:= x;

end loop

```

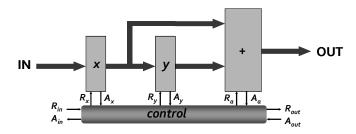

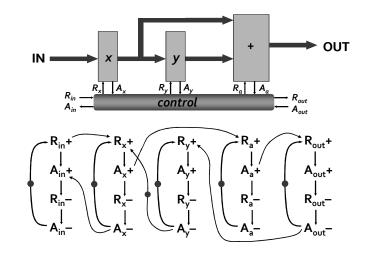

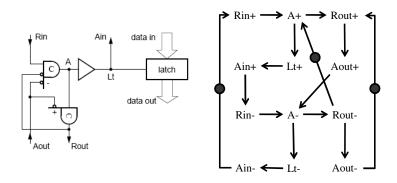

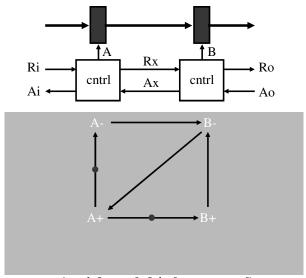

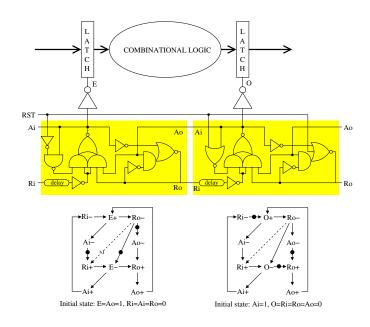

## A simple filter: block diagram

- x and y are level-sensitive latches (transparent when R=1)

- + is a bundled-data adder (matched delay between  $R_a$  and  $A_a$ )

- R<sub>in</sub> indicates the validity of IN

- After A<sub>in</sub>+ the environment is allowed to change IN

- (Route Aout) control a level-sensitive latch at the output

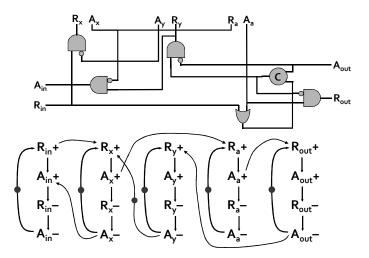

## A simple filter: control spec.

## A simple filter: control impl.

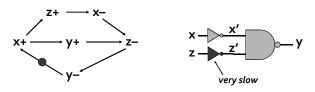

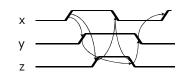

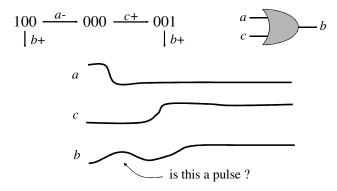

## Taking delays into account

Delay assumptions: unbounded delays

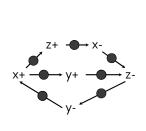

events:  $x+ \rightarrow x'- \rightarrow y+ \rightarrow z+ \rightarrow x- \rightarrow x'+ \rightarrow y-$  failure! time: 3 4 5 6 9 10 11

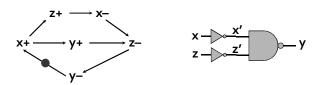

## Taking delays into account

Delay assumptions:

- Environment: 3 time units

- Gates: 1 time unit

events:  $x+ \rightarrow x'- \rightarrow y+ \rightarrow z+ \rightarrow z'- \rightarrow x- \rightarrow x'+ \rightarrow z- \rightarrow z'+ \rightarrow y- \rightarrow$ time: 3 4 5 6 7 9 10 12 13 14

#### WHY ASYNCHRONOUS

#### Motivation (designer's view)

- Modularity for system-on-chip design

- Plug-and-play interconnectivity

- Average-case peformance

- No worst-case delay synchronization

- Many interfaces are asynchronous

- Buses, networks, ...

#### **Dissuasion**

- Concurrent models for specification

- CSP, Petri nets, ...: no more FSMs

- Difficult to design

- Hazards, synchronization

- Complex timing analysis

- Difficult to estimate performance

- Difficult to test

- No way to stop the clock

#### Motivation (technology aspects)

- Low power

- Automatic clock gating

- Electromagnetic compatibility

- No peak currents around clock edges

- Security

- No 'electro-magnetic difference' between logical 'o' and '1'in dual rail code

- Robustness

- High immunity to technology and environment variations (temperature, power supply, ...)

## SYNTHESIS OF ASYNCHRONOUS CIRCUITS FROM PETRI NETS

#### Delay models (II)

- Separation between functionality and timing [Muller]

- Every gate has a zero-delay atomic evaluator (Boolean function)

- A delay is associated to every output (gate delay model) or every input (wire delay model)

- Delays can be:

- Unbounded (arbitrary finite delays)

- Bounded (within given min/max bounds)

Gate delay model

Wire delay model

#### Delay models (I)

Abstractions are necessary to define delay models manageable for design, synthesis and verification. Abstractions introduce optimistic and pessimistic simplifications that must be carefully taken into account.

#### Delay models (III)

• Gate delay model: delays in gates, no delays in wires

Wire delay model: delays in gates and wires

#### Delay models (IV)

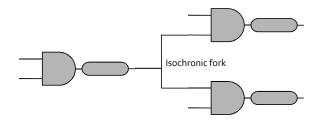

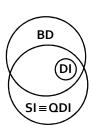

- Speed-independent circuit: hazard-free under the unbounded gate delay model

- Delay-insensitive circuit: hazard-free under the unbounded wire delay model

- Quasi-delay-insensitive circuit: delay-insensitive with some isochronic forks

#### Fundamental mode of operation

[Huffman 1964] : The circuit/environment interact with two phases

- (1) The environment sends inputs to the circuit

- (2) The circuit computes the outputs and the state signals

The environment does not send new inputs until the circuit stabilizes

Normal Fundamental Mode: Only one input changes at each communication cycle

#### Speed-independent model

- Pessimistic, since delays are typically bounded

- Optimistic, since it assumes isochronic forks (negligible skew wrt the receiving gate delays)

- Efficient synthesis methods exist

#### Input/Output mode of operation

- Computation and communication can overlap (according to some specified protocol)

- Event-based specification models are often used to describe the behavior (e.g., Petri nets).

This tutorial will cover the synthesis of speed-independent circuits that work under the I/O mode of operation and are specified using Petri nets.

#### Delay models for async. circuits

- Bounded delays (BD): realistic for gates and wires.

- Technology mapping is easy, verification is difficult

- Speed independent (SI): Unbounded (pessimistic) delays for gates and "negligible" (optimistic) delays for wires.

- Technology mapping is more difficult, verification is easy

- Delay insensitive (DI): Unbounded (pessimistic) delays for gates and wires.

- DI class (built out of basic gates) is almost empty

- Quasi-delay insensitive (QDI): Delay insensitive except for critical wire forks (isochronic forks).

- In practice it is the same as speed independent

#### Book and synthesis tool

- J. Cortadella, M. Kishinevsky, A. Kondratyev,

L. Lavagno and A. Yakovlev,

Logic synthesis for asynchronous

controllers and interfaces,

Springer-Verlag, 2002

- petrify: http://www.lsi.upc.es/petrify

#### **Outline**

- Overview of the synthesis flow

- Specification

- State graph and next-state functions

- State encoding

- Implementability conditions

- Speed-independent circuit

- Complex gates

- C-element architecture

- Review of some advanced topics

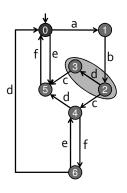

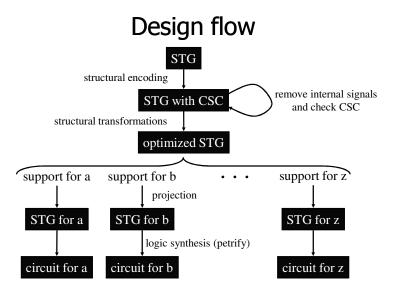

#### Design flow

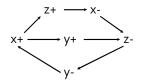

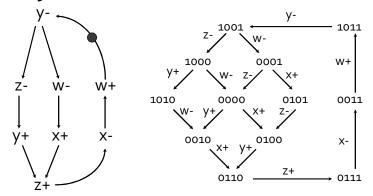

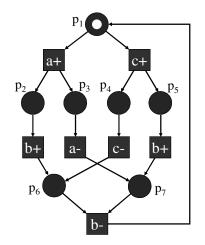

## Specification

Signal Transition Graph (STG)

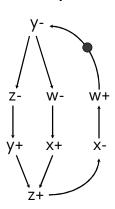

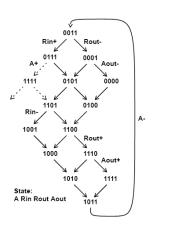

#### Token flow

## State graph

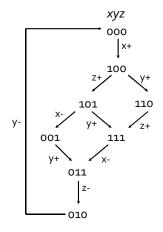

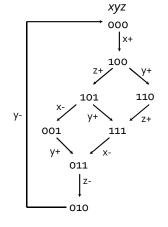

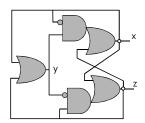

#### Next-state functions

$$y = z + x$$

$$z = x + \overline{y} \cdot z$$

#### Gate netlist

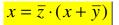

$$x = \overline{z} \cdot (x + \overline{y})$$

$$y = z + y$$

$$z = x + \overline{y} \cdot z$$

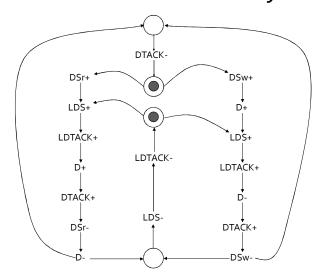

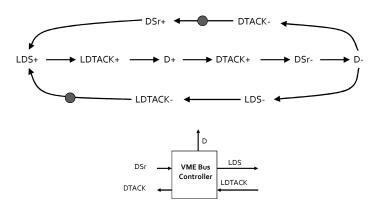

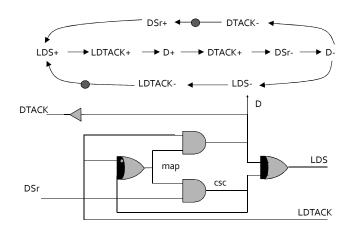

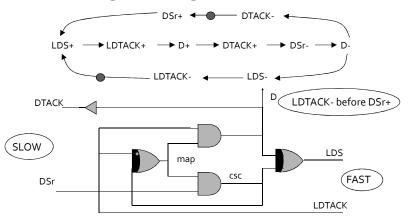

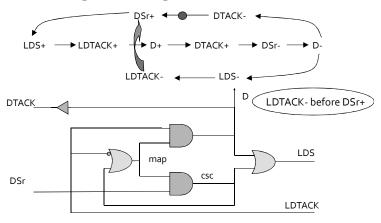

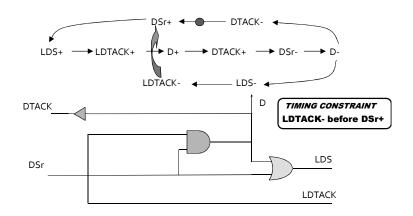

#### VME bus

## Design flow

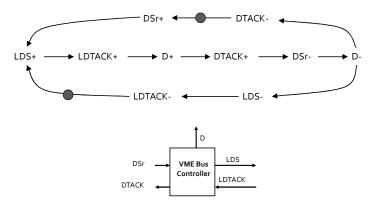

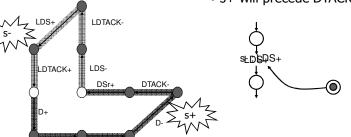

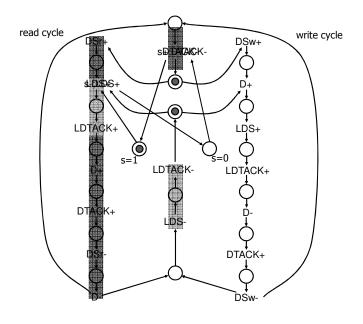

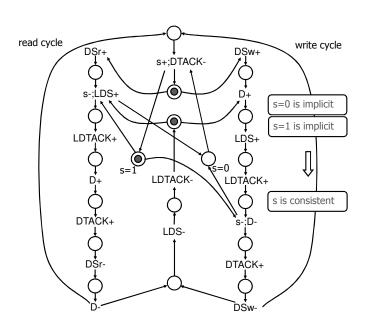

## STG for the READ cycle

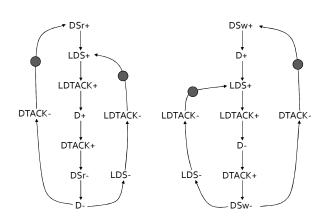

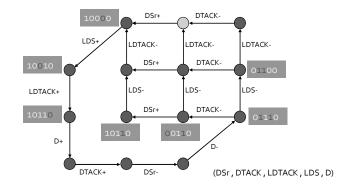

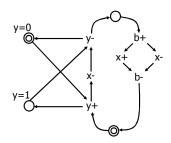

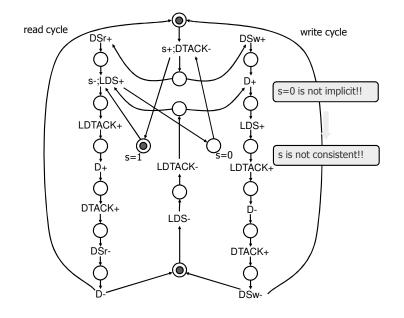

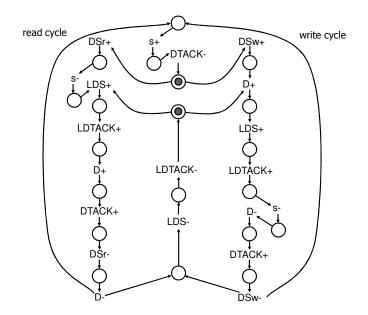

## Choice: Read and Write cycles

#### Circuit synthesis

- Goal:

- Derive a hazard-free circuit under a given delay model and mode of operation

#### Choice: Read and Write cycles

#### Speed independence

- Delay model

- Unbounded gate / environment delays

- Certain wire delays shorter than certain paths in the circuit

- Conditions for implementability:

- Consistency

- Complete State Coding

- Persistency

#### Design flow

#### STG for the READ cycle

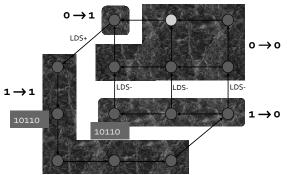

## Binary encoding of signals

## Binary encoding of signals

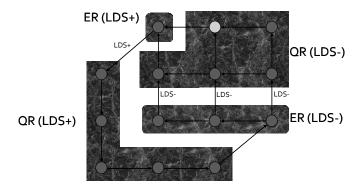

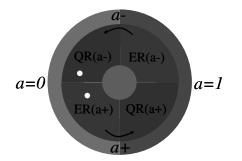

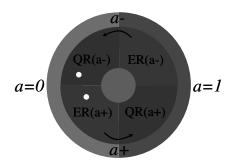

#### Excitation / Quiescent Regions

Next-state function

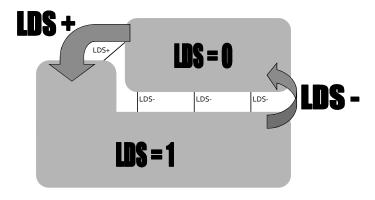

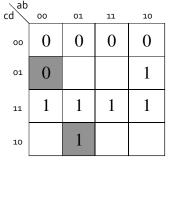

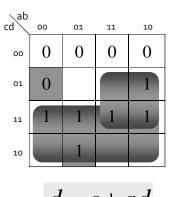

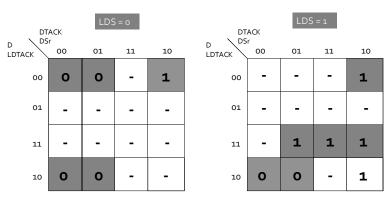

## Karnaugh map for LDS

## Design flow

## Concurrency reduction

## Concurrency reduction

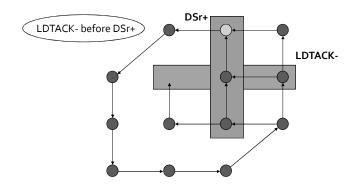

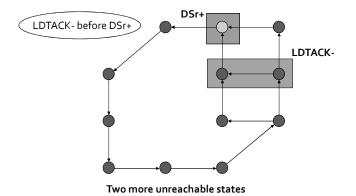

## State encoding conflicts

## Signal Insertion

#### Design flow

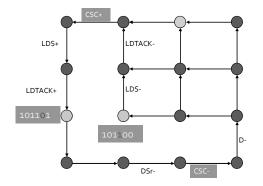

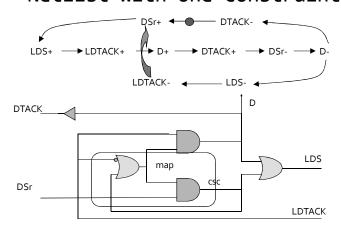

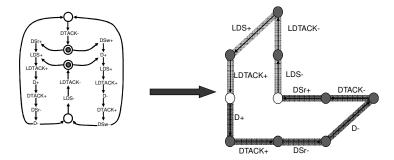

#### Complex-gate implementation

$$LDS = D + \csc$$

$$DTACK = D$$

$$D = LDTACK \cdot \csc$$

$$\csc = DSr \cdot (\csc + \overline{LDTACK})$$

#### Implementability conditions

- Consistency

- Rising and falling transitions of each signal alternate in any trace

- Complete state coding (CSC)

- Next-state functions correctly defined

- Persistency

- No event can be disabled by another event (unless they are both inputs)

## Implementability conditions

Consistency + CSC + persistency

There exists a speed-independent circuit that implements the behavior of the STG

(under the assumption that ay Boolean function can be implemented with one complex gate)

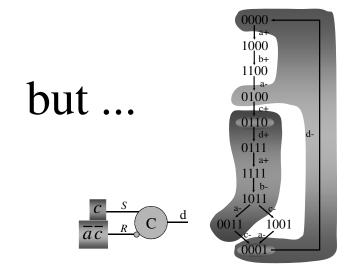

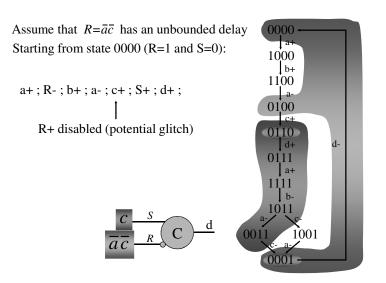

## Persistency

Speed independence ⇒ glitch-free output behavior under any delay

Complex gate

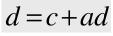

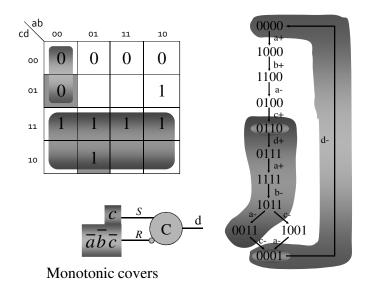

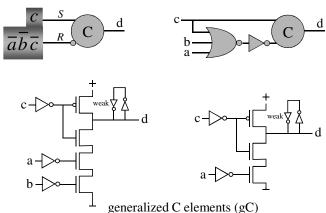

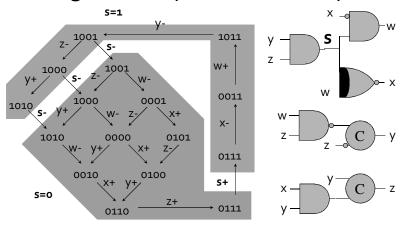

#### Implementation with C elements

$$\bullet \bullet \bullet \to S+ \to z+ \to S- \to R+ \to z- \to R- \to \bullet \bullet$$

- S (set) and R (reset) must be mutually exclusive

- S must cover ER(z+) and must not intersect  $ER(z-) \cup QR(z-)$

- R must cover ER(z-) and must not intersect  $ER(z+) \cup QR(z+)$

#### C-based implementations

## Speed-independent implementations

- Implementability conditions

- Consistency

- Complete state coding

- Persistency

- Circuit architectures

- Complex (hazard-free) gates

- C elements with monotonic covers

· ...

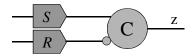

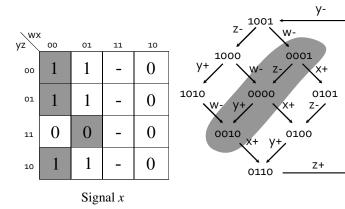

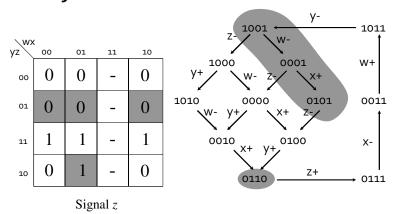

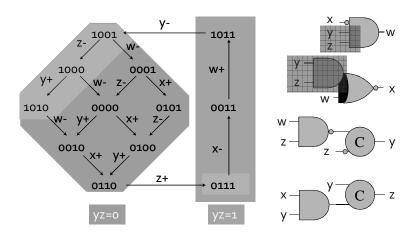

## Synthesis exercise

Derive circuits for signals x and z (complex gates and monotonic covers)

## Synthesis exercise

## Synthesis exercise

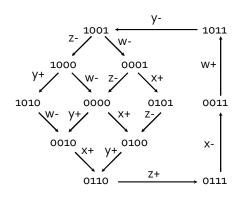

## Logic decomposition: example

1011

0011

## Logic decomposition: example

## Logic decomposition: example

## Logic decomposition: example

## Speed-independent Netlist

## Adding timing assumptions

## Adding timing assumptions

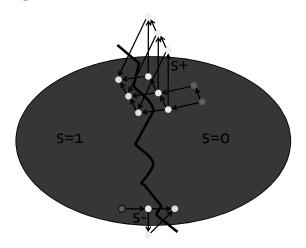

## State space domain

## State space domain

## State space domain

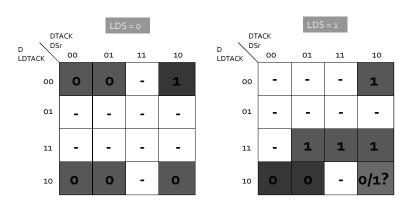

#### Boolean domain

| LDS = 0 |   |    |    |    | LDS = 1 |   |    |    |      |

|---------|---|----|----|----|---------|---|----|----|------|

| D DS    |   | 01 | 11 | 10 | D DS    |   | 01 | 11 | 10   |

| 00      | 0 | 0  | -  | 1  | 00      | - | -  | -  | 1    |

| 01      | - | -  | -  | •  | 01      | - | -  | 1  | -    |

| 11      | - | -  | •  | ı  | 11      | - | 1  | 1  | 1    |

| 10      | 0 | 0  | -  | 0  | 10      | 0 | 0  | -  | 0/1? |

#### Boolean domain

One more DC vector for *all* signals

One state conflict is removed

#### Netlist with one constraint

#### Netlist with one constraint

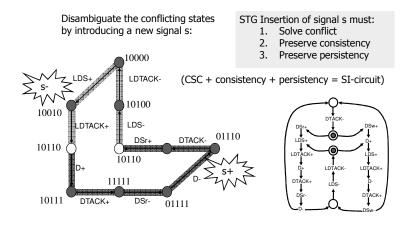

#### Signal insertion

- New signals need to be inserted to solve some synthesis problems (e.g., state encoding, logic decomposition)

- For each signal s, the events s+ and s- must be inserted while preserving certain behavioral properties (consistency, persistency).

- Each new signal determines a new partition of states (s=0, s=1)

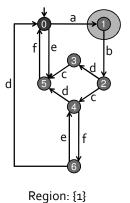

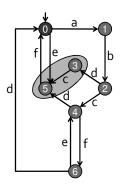

#### From state graphs to Petri nets

- A state graph may require transformations to meet certain properties (e.g., state encoding).

- The visualization of a state graph is not very informative. Event-based specifications explicitly represent the relations between events.

- Resort to the theory of regions

#### Signal insertion

#### From state graphs to Petri nets

#### From state graphs to Petri nets

#### From state graphs to Petri nets

Not a region: {3,5}

#### From state graphs to Petri nets

#### Theory of regions

- Region: all arcs of any event have the same relationship with the region (enter, exit, no cross).

- Minimal region: not included in any other region

- Pre-/post-region of an event: region such that the event exits/enters the region

- Property: excitation closure

- The intersection of all pre-regions of an event is the excitation region of the event

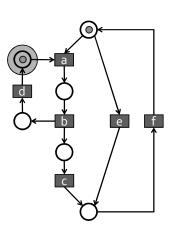

#### OTHER PARADIGMS

Thanks to Steve Nowick (Columbia Univ.)

## Burst-Mode Specifications

Example: Burst-Mode (BM) Specification:

- Inputs in specified **"input burst"** can arrive <u>in any order</u> and <u>at any time</u>

- After all inputs arrive, generate "output burst"

#### Note:

-input bursts: must be <u>non-empty</u>

(at least 1 input per burst)

-output bursts: may be empty

(o or more outputs per burst)

**Initial Values:**

#### Burst-Mode Specifications/ How to specify "burst-mode" behavior?: current state A+ C-/ Y- Z+ input burst/ output burst next state inputs outputs Hazard-Free Combinational Network output burst input burst (several bits)

#### Burst-Mode Specifications

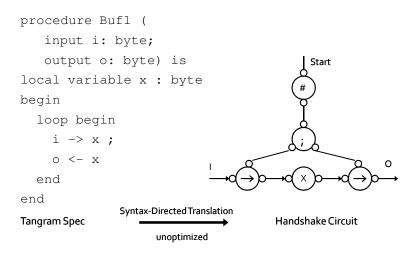

#### Syntax-directed translation

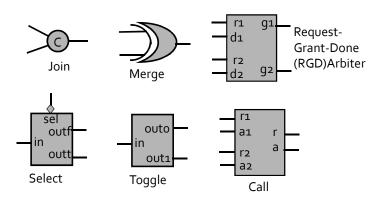

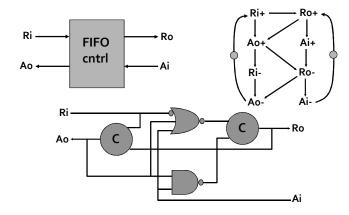

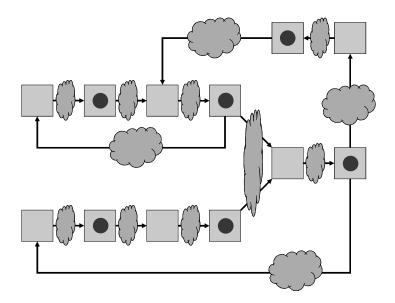

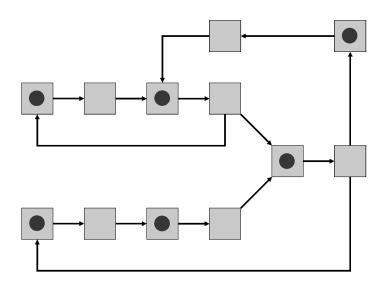

#### 2-Place "Ripple Register" (= FIFO) [van Berkel]

####

## A Larger Example

Intermediate

"Handshake Circuit"

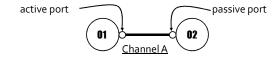

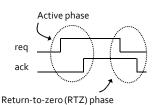

#### Background: Channel-Based Communication

#### Components communicate using "4-phase handshaking"

**O1:** <u>initiates</u> communication

❖ O2: <u>completes</u> communication

#### Channel impltn. => <u>use 2 wires</u>:

req => start operation

ack => operation done

(... can be extended to handle data)

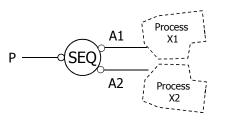

#### Handshake Components: Sequencer

<u>**2-Way Sequencer:**</u> activated on channel P; then activates 2 processes in sequence on channels A1 and A2

Operation X1; X2

Goal: activate two sequential processes (i.e. operations)

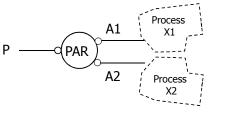

#### Handshake Components: PAR Component

PAR Component: activated on channel P;

then activates 2 processes in parallel on channels A1 and A2

Operation X1 || X2

Goal: activate two parallel processes

#### Conclusions

- STGs have a high expressiveness power at a low level of granularity (similar to FSMs for synchronous systems)

- Synthesis from STGs can be fully automated

- Synthesis tools often suffer from the state explosion problem (symbolic techniques are used)

- The theory of logic synthesis from STGs can be found in:

J. Cortadella, M. Kishinevsky, A. Kondratyev, L. Lavagno and A. Yakovlev, Logic Synthesis of Asynchronous Controllers and Interfaces, Springer Verlag, 2002.

#### Intermediate Representation

# Structural methods for synthesis of large specifications

Thanks to Josep Carmona and Victor Khomenko

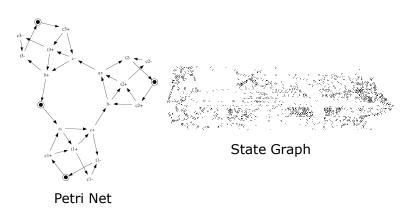

#### State space explosion problem

- ► Even in bounded nets, the state space can be exponential on the size of the net

- Concurrency (explosion of interleavings)

#### **Outline**

- ► Structural theory of Petri nets

- Marking equation

- Invariants

- ▶ ILP methods based on the marking equation

- Detection of state encoding conflicts

- Synthesis

- ► Methods based on unfoldings

#### Event-based vs. State-based model

#### Marking equation

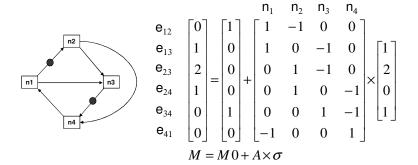

#### Incidence matrix

## Marking equation

#### M' = M + Ax

Necessary reachability condition, but not sufficient.

### Spurious markings

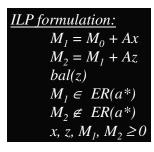

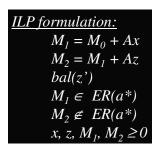

## **Checking Unique State Coding**

$$M_0 \xrightarrow{x} M_1 \xrightarrow{z = \{a+b+a-b-\}} M_2$$

- M<sub>1</sub> and M<sub>2</sub> have the same binary code (z must be a complementary set of transitions)

- M<sub>1</sub> and M<sub>2</sub> must be different markings (they must differ in at least one place)

#### **Checking Unique State Coding**

$$M_0 \xrightarrow{x} M_1 \xrightarrow{z = \{a+b+a-b-\}} M_2$$

$$\begin{split} \underline{ILP\ formulation:} \\ M_1 &= M_0 + Ax \\ M_2 &= M_1 + Az \\ bal(z) \\ M_1 \neq M_2 \\ x, z, M_1, M_2 \geq 0 \end{split}$$

$bal(z) \equiv \forall a: \#(a+) - \#(a-) = 0$

#### Some experiments (USC)

| benchmark      | P   | T  | signals | CPU(s) |

|----------------|-----|----|---------|--------|

| PpWk(3,9)      | 106 | 56 | 28      | 0.03   |

| PpWk(3,12)     | 142 | 74 | 37      | 0.05   |

| PpWkCsc(3,9)   | 108 | 56 | 28      | 0.67   |

| PpWkCsc(3,12)  | 144 | 74 | 37      | 1.17   |

| PpArb(3,9)     | 128 | 72 | 34      | 0.06   |

| PpArb(3,12)    | 164 | 90 | 43      | 0.08   |

| PpArbCsc(3,9)  | 131 | 72 | 34      | 1.05   |

| PpArbCsc(3,12) | 167 | 90 | 43      | 1.69   |

## **Checking Complete State Coding**

n ILP problems must be solved(n is the number of transitions with label a\*)

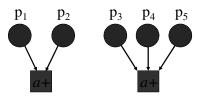

## **Enabling conditions in ILP**

$M \in ER(a+): M(p_1)+M(p_2) \ge 2 \quad \lor \quad M(p_3)+M(p_4)+M(p_5) \ge 3$

$M \notin ER(a+): M(p_1)+M(p_2) \le 1 \land M(p_3)+M(p_4)+M(p_5) \le 2$

(\*formulation for safe nets only)

## Some experiments (CSC)

| benchmark    | P    | T    | signals | CLP    | SAT    | ILP   |

|--------------|------|------|---------|--------|--------|-------|

| Tangram(3,2) | 142  | 92   | 38      | 0.01   | 0.01   | 1.08  |

| Tangram(4,3) | 321  | 202  | 83      | 0.06   | 0.04   | 9.00  |

| Art(10,9)    | 216  | 198  | 99      | 0.00   | 0.42   | 0.06  |

| Art(20,9)    | 436  | 398  | 199     | 5.00   | 10.35  | 0.24  |

| Art(30,9)    | 656  | 598  | 299     | 38.02  | 81.82  | 0.56  |

| Art(40,9)    | 876  | 798  | 399     | 138.04 | 264.57 | 0.92  |

| Art(50,9)    | 1096 | 998  | 499     | 377.00 | 630.41 | 1.46  |

| ArtCsc(10,9) | 752  | 630  | 315     | time   | 14 m   | 3 m   |

| ArtCsc(20,9) | 1532 | 1270 | 635     | time   | mem    | 27 m  |

| ArtCsc(30,9) | 2312 | 1910 | 955     | time   | mem    | 1.5 h |

| ArtCsc(40,9) | 3092 | 2550 | 1275    | time   | mem    | 3.5 h |

| ArtCsc(50,9) | 3872 | 3190 | 1595    | time   | mem    | 7 h   |

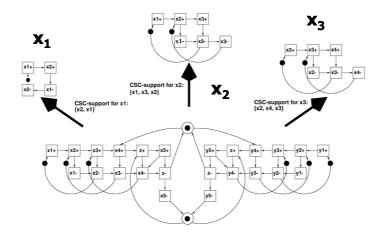

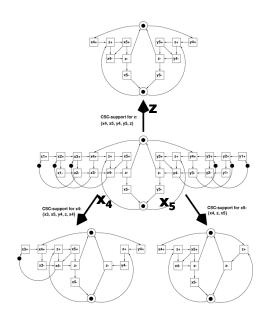

## **Synthesis**

- ► Each signal can be implemented with a subset of the STG signals in the support (typically less than 10)

- ► Synthesis of a signal:

- Project the STG onto the support signals (hide the rest)

- After projection, the STG still has CSC for the signal

- Use state-based methods on each projection

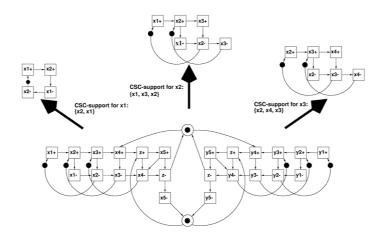

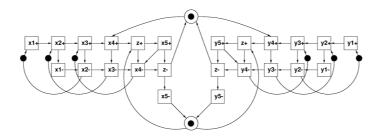

## Synthesis example

#### Checking the support for a signal

Let  $\Sigma$  be the set of signals and  $\Sigma$ ' a potential support for a. Let z' be the projection of z onto  $\Sigma$ '.

$\Sigma$ ' is a valid support for a if the following model has no solution:

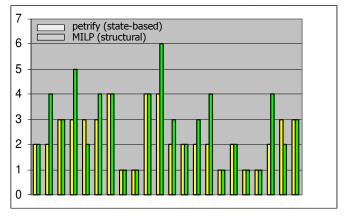

#### Experiments (Support + Synthesis)

|                 | 0                   | IDI |     |         |          |     |         |     |

|-----------------|---------------------|-----|-----|---------|----------|-----|---------|-----|

| benchmark       | States              | P   | T   | signals | Literals |     | CPU     |     |

|                 |                     |     |     |         | Petrify  | ILP | Petrify | ILP |

| PpWkCsc(2,6)    | 8192                | 47  | 26  | 19      | 57       | 57  | 5       | 1   |

| PpWkCsc(2,9)    | 524288              | 71  | 38  | 19      | 87       | 87  | 49      | 2   |

| PpWkCsc(3,9)    | 2.7 x 10E7          | 106 | 56  | 28      | ?        | 130 | mem     | 3   |

| PpWkCsc(3,12)   | 2.2 x 10E11         | 142 | 74  | 37      | ?        | 117 | time    | 3   |

| PpArbCsc(2,6)   | 61440               | 62  | 36  | 17      | 77       | 77  | 21      | 83  |

| PpArbCsc(2,9)   | 3.9 x 10 <b>E</b> 6 | 110 | 60  | 29      | 107      | 107 | 185     | 59  |

| PpArbCsc(3,9)   | 3.3 x 10E9          | 131 | 72  | 34      | 163      | 165 | 10336   | 289 |

| PpArbCsc(3,12)  | 1.7 x 10E12         | 167 | 90  | 43      | ?        | 210 | time    | 608 |

| TangramCsc(3,2) | 426                 | 142 | 92  | 38      | 97       | 103 | 56      | 146 |

| TangramCsc(4,3) | 9258                | 321 | 202 | 83      | ?        | 247 | mem     | 2 h |

- ► Petrify (*Cortadella et al* ):

- State-based & technology mapping

- BDD

#### Algorithm to find the support

```

z' := \{a\} \cup \{\text{trigger signals of a}\};

\begin{array}{l} & \text{forever} \\ & z'' := ILP\_\text{check\_support (STG, a, z');} \\ & & \text{if } z'' = 0 \text{ then return } z'; \\ & & z' := z' \cup \{\text{unbalanced signals in } z''\}; \end{array}

\text{end forever}

```

## Synthesis example

#### **STATE ENCODING**

## Detection of conflicting states

- ILP

- [Carmona & Cortadella, ICCAD'03]

- SAT-UNFOLD [Khomenko *et al.*, Fund. Informaticae]

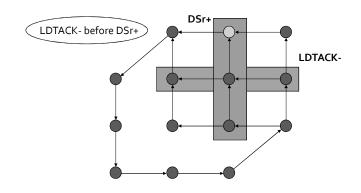

#### Disambiguation by consistent signal insertion

#### Implicit place

DEF1 (Behavior): The behavior of the net does not depend on the place.

DEF2 (Petri net): it never disables the firing of a transition.

#### Consistency

Consecutive firings of a signal must alternate

#### Implicit Places & Consistency

Theorem (Colom *et al.*)

Places y=0 and y=1 are implicit *if and only if* signal y is consistent

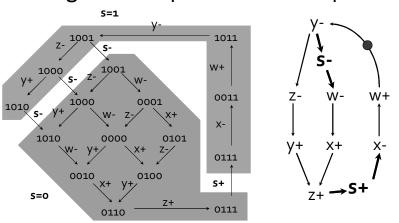

#### Disambiguation by consistent signal insertion

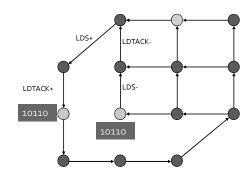

Disambiguate the conflicting states by introducing a new signal s:

DTACK+

Insertion of s into the STG:

• s- will precede LDS+

• s+ will precede DTACK-

#### Main algorithm for solving CSC conflicts

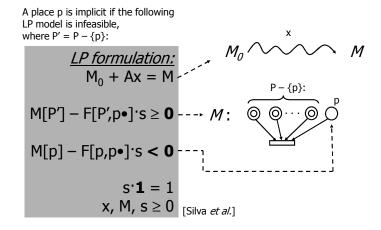

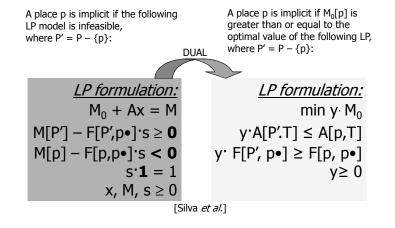

#### LP model to check place implicitness

#### State space explosion problem

- ► Goal: avoid state enumeration to check implicitness of a place.

- ► Classical methods to avoid the explicit state space enumeration:

- Linear Algebra (LP/MILP)

Structural methods

- Graph Theory

- Symbolic representation (BDDs)

- Partiar order (Unfoldings)

#### LP model to check place implicitness

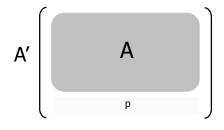

#### MILP model to insert a implicit place

## MILP model to find insertion points that disambiguate the conflict

$\begin{array}{c} \underline{\textit{MILP formulation:}} \\ \text{MILP "s=0 implicit"} \\ \text{MILP "s=1 implicit"} \\ \#(\sigma_1, s+) = \#(\sigma_1, s-) + 1 \\ \#(\sigma_2, s-) = \#(\sigma_2, s+) + 1 \\ \text{M}_0[s=0] + \text{M}_0[s=1] = 1 \end{array}$

If there is a solution, rows in A' for s=0 and s=1 describe the insertion points (arcs in the net)

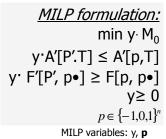

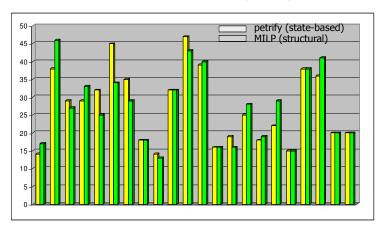

#### Number of inserted encoding signals

Benchmarks from [Cortadella et al., IEEE TCAD'97]

#### Number of literals (area)

Benchmarks from [Cortadella et al., IEEE TCAD'97]

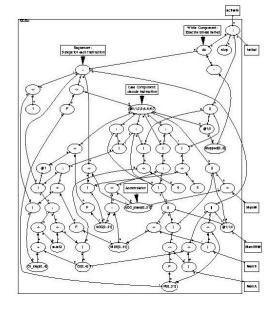

#### Experimental results: large controllers

| Places | Trans                                               | Signals                                                                          | CPU(min)                                                                                                                                                                | #sig                                                                                                                                                                                                                                                                | Lits                                                                                                                                                                                                                                                                                                                      | HDL                                                                                                                                                                                                                                                                                                                                                                                       |

|--------|-----------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 216    | 198                                                 | 99                                                                               | 3.6                                                                                                                                                                     | 28                                                                                                                                                                                                                                                                  | 305                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                         |

| 436    | 398                                                 | 199                                                                              | 73.0                                                                                                                                                                    | 57                                                                                                                                                                                                                                                                  | 629                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                         |

| 142    | 74                                                  | 37                                                                               | 1.0                                                                                                                                                                     | 3                                                                                                                                                                                                                                                                   | 190                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                         |

| 164    | 90                                                  | 43                                                                               | 11.5                                                                                                                                                                    | 2                                                                                                                                                                                                                                                                   | 206                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                         |

| 302    | 338                                                 | 150                                                                              | 6.4                                                                                                                                                                     | 24                                                                                                                                                                                                                                                                  | 613                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                         |

| 368    | 394                                                 | 183                                                                              | 12.7                                                                                                                                                                    | 27                                                                                                                                                                                                                                                                  | 445                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                         |

| 63     | 52                                                  | 52                                                                               | 0.2                                                                                                                                                                     | 12                                                                                                                                                                                                                                                                  | 101                                                                                                                                                                                                                                                                                                                       | 253                                                                                                                                                                                                                                                                                                                                                                                       |

| 160    | 128                                                 | 64                                                                               | 2.2                                                                                                                                                                     | 23                                                                                                                                                                                                                                                                  | 269                                                                                                                                                                                                                                                                                                                       | 398                                                                                                                                                                                                                                                                                                                                                                                       |

| 192    | 394                                                 | 60                                                                               | 11.8                                                                                                                                                                    | 17                                                                                                                                                                                                                                                                  | 237                                                                                                                                                                                                                                                                                                                       | 640                                                                                                                                                                                                                                                                                                                                                                                       |

|        | 216<br>436<br>142<br>164<br>302<br>368<br>63<br>160 | 216 198<br>436 398<br>142 74<br>164 90<br>302 338<br>368 394<br>63 52<br>160 128 | 436     398     199       142     74     37       164     90     43       302     338     150       368     394     183       63     52     52       160     128     64 | 216     198     99     3.6       436     398     199     73.0       142     74     37     1.0       164     90     43     11.5       302     338     150     6.4       368     394     183     12.7       63     52     52     0.2       160     128     64     2.2 | 216     198     99     3.6     28       436     398     199     73.0     57       142     74     37     1.0     3       164     90     43     11.5     2       302     338     150     6.4     24       368     394     183     12.7     27       63     52     52     0.2     12       160     128     64     2.2     23 | 216     198     99     3.6     28     305       436     398     199     73.0     57     629       142     74     37     1.0     3     190       164     90     43     11.5     2     206       302     338     150     6.4     24     613       368     394     183     12.7     27     445       63     52     52     0.2     12     101       160     128     64     2.2     23     269 |

Synthesis with structural methods from [Carmona & Cortadella, ICCAD'03]

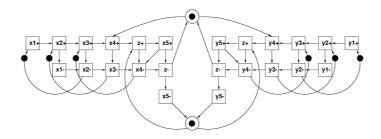

## SYNTHESIS USING UNFOLDINGS

Work by Khomenko, Koutny and Yakovlev

## It doesn't always work ...

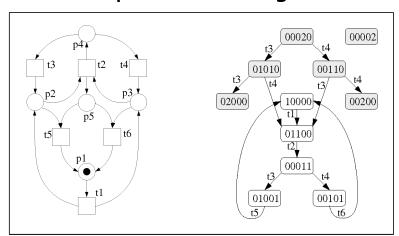

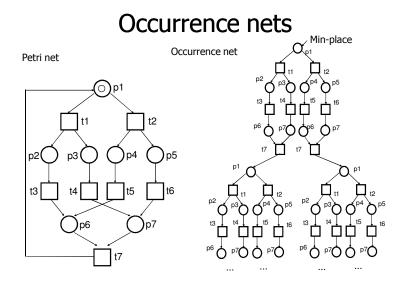

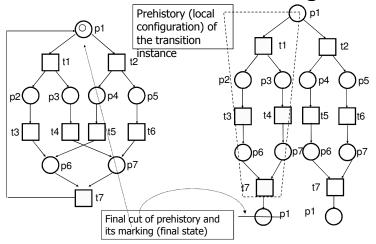

#### Occurrence nets

- ► The occurrence net of a PN N is a labelled (with names of the places and transitions of N) net (possibly infinite!) which is:

- Acyclic

- Contains no backward conflicts (1)

- No transition is in self-conflict (2)

- No twin transitions (3)

- Finitely preceded (4)

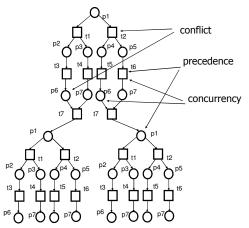

#### Relations in occurrence nets

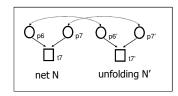

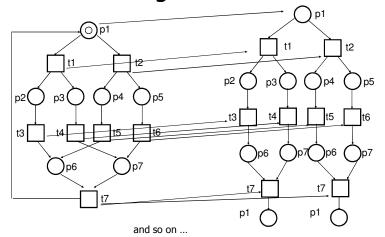

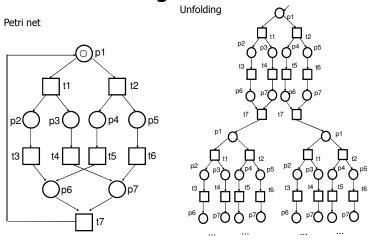

## Unfolding of a PN

- ► The unfolding of Petri net *N* is a maximal labelled occurrence net (up to isomorphism) that preserves:

- one-to-one correspondence (bijection) between the predecessors and successors of transitions with those in the original net

- bijection between min places and the initial marking elements (which is multi-set)

#### **Unfolding construction**

## Unfolding construction Unfolding Construction

## Petri net and its unfolding

## Petri net and its unfolding

### Petri net and its unfolding

## Petri net and its unfolding

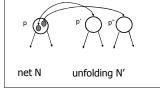

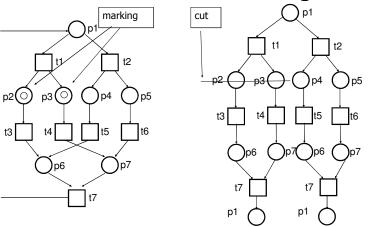

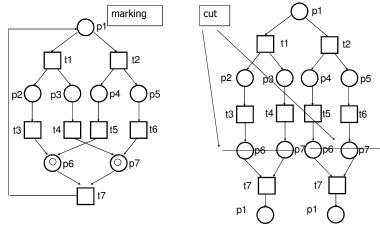

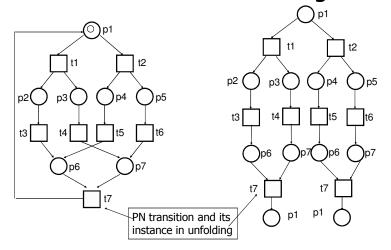

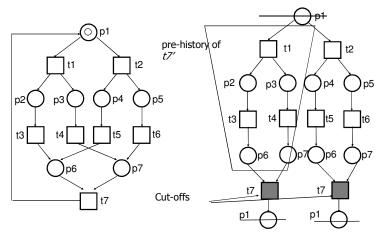

#### Truncation of unfolding

- ► At some point of unfolding the process begins to repeat parts of the net that have already been instantiated

- ► In many cases this also repeats the markings in the form of cuts

- ► The process can be stopped in every such situation

- ► Transitions which generate repeated cuts are called cut-off points or simply *cut-offs*

- ▶ The unfolding truncated by cut-off is called *prefix*

#### **Cutoff transitions**

####

lds-

10110

dsr+

lds-

00110

dtack-

lds-

01110

ldtack+

10110

## Example: enforcing CSC

#### **Unfoldings**

- © Alleviate the state space explosion problem

- More visual than state graphs

- © Proven efficient for model checking

- ⊗ Quite complicated theory

- Not sufficiently investigated

- Relatively few algorithms

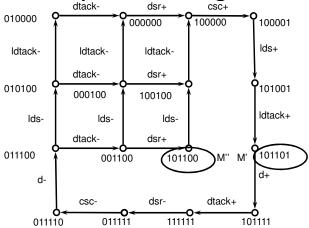

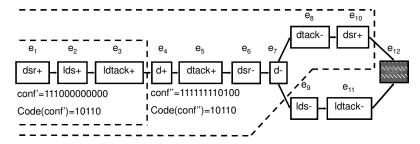

#### Translation Into a SAT Problem

- ► Configuration constraint: conf' and conf" are configurations

- ► Encoding constraint: Code(conf') = Code(conf'')

- ► Separating constraint: Out(conf') ≠ Out(conf")

#### Translation Into a SAT Problem

Conf(conf') ∧ Conf(conf") ∧

Code(conf',..., val) ∧ Code(conf ",..., val) ∧

Out(conf',..., out') ∧ Out(conf ",..., out") ∧

out'≠ out"

## Configuration constraint

$$\bigwedge_{f \in ({}^{\bullet}e)^{\bullet} \setminus \{e\}} \neg (conf_e \land conf_f)$$

no conflicts

## Tracing the value of a signal

## Computing the signals' values

$$cut_b \Leftrightarrow conf_e \land \bigwedge_{f \in b} \neg conf_f$$

$$|val_z \Leftrightarrow \bigvee_{h(b)=p_{z=1}} cut_b$$

## Computing the enabled outputs

$$en_e \Leftrightarrow \bigwedge_{f \in {}^{\bullet}({}^{\bullet}e)} conf_f \land \bigwedge_{f \in ({}^{\bullet}e)} \neg conf_f$$

$$out_z \Leftrightarrow \bigvee_{h(e)=z^{\pm}} en_e$$

## Analysis of the Method

- ⊕ A lot of clauses of length 2 good for BCP

- The method can be generalized to other coding properties, e.g. USC and normalcy

- The method can be generalized to nets with dummy transitions

- © Further optimization is possible for certain net subclasses, e.g. unique-choice nets

#### **Experimental Results**

- ► Unfoldings of STGs are almost always small in practice and thus well-suited for synthesis

- ► Huge memory savings

- ► Dramatic speedups

- ► Every valid speed-independent solution can be obtained using this method, so no loss of quality

- ▶ We can trade off quality for speed (e.g. consider only minimal supports): in our experiments, the solutions are the same as Petrify's (up to Boolean minimization)

- ► Multiple implementations produced

#### Synthesis using unfoldings

for each output signal z

#### compute (minimal) supports of z

for each 'promising' support X

compute the projection of the set of reachable encodings onto X sorting them according to the corresponding values of  $\mathrm{Nxt_z}$

apply Boolean minimization to the obtained ON- and OFF-sets

choose the best implementation of z

#### ILP vs. Unfoldings

- ►TIP:

- Efficient in runtime

- Incomplete (spurious markings)

- **►** Unfoldings:

- Efficient in runtime (but slower than ILP)

- Complete

- ► Both methods give synthesis results similar to state-based methods

## Direct synthesis (Varshavsky's Approach)

## Direct synthesis

## Direct synthesis

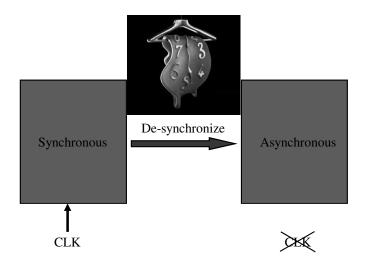

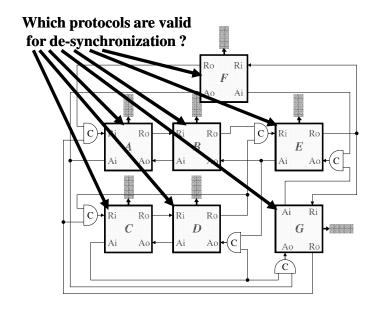

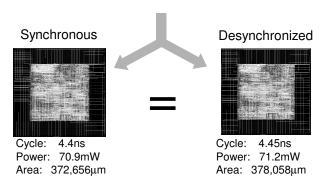

## De-synchronization: from synchronous to asynchronous

#### Based on the paper:

Blunno, Cortadella, Kondratyev, Lavagno, Lwin, Sotiriou, *Handshake protocols for de-synchronization*, ASYNC 2004.

#### Outline

- What is de-synchronization?

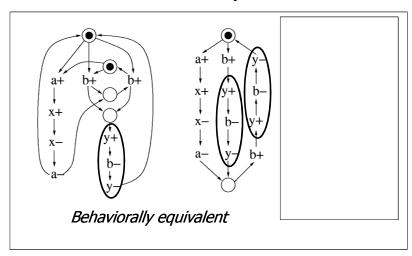

- Behavioral equivalence

- 4-phase protocols for de-synchronization

- **■** Concurrency

- **■** Correctness

- An example

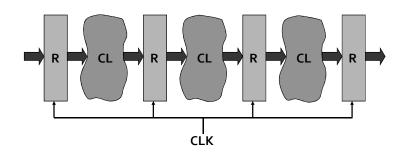

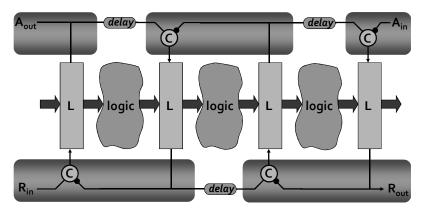

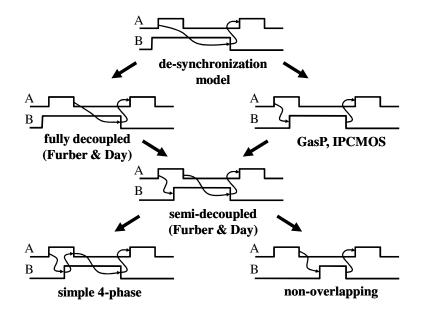

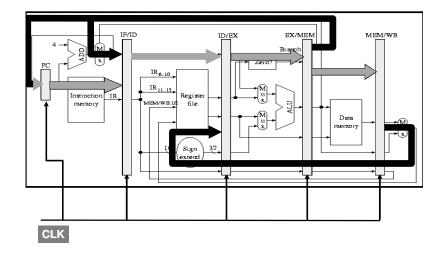

### Synchronous circuit

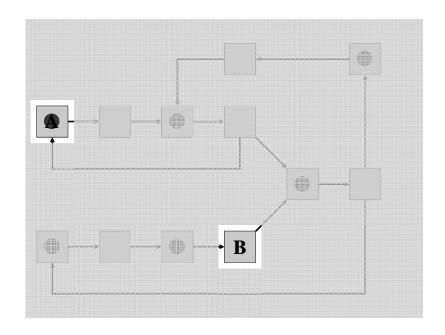

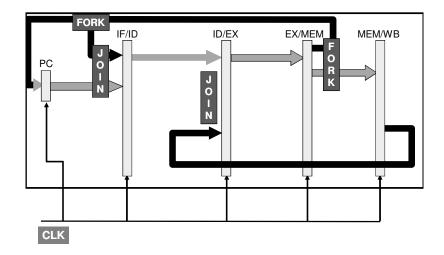

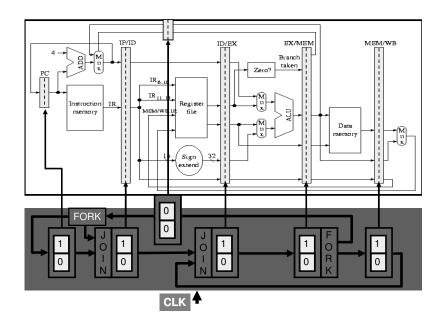

### De-synchronization

#### Design flow

- Think synchronous

- Design synchronous: one clock and edge-triggered flip-flops

- De-synchronize (automatically)

- Run it asynchronously

#### De-synchronization

Distributed controllers substitute the clock network

The data path remains intact!

#### Prior work

- Micropipelines (Sutherland, 1989)

- Local generation of clocks

- ♦ Varshavsky et al., 1995

- ♦ Kol and Ginosar, 1996

- Theseus Logic (Ligthart et al., 2000)

- ◆ Commercial HDL synthesis tools

- $\ \, \mbox{\Large }$  Direct translation and special registers

- Phased logic (Linder and Harden, 1996) (Reese, Thornton, Traver, 2003)

- ◆ Conceptually similar

- Different handshake protocol (2 phase vs. 4 phase)

#### Automatic de-synchronization

- Devise an *automatic method* for de-synchronization

- Identify a *subclass of synchronous circuits* suitable for de-synchronization

- Formally prove correctness

#### Outline

- What is de-synchronization?

- Behavioral equivalence

- 4-phase protocols for de-synchronization

- **■** Concurrency

- **■** Correctness

- An example

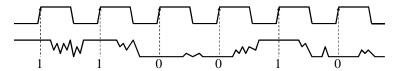

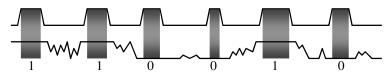

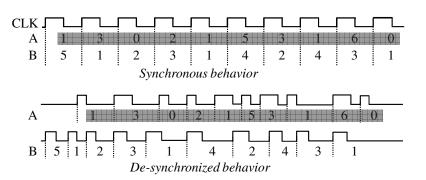

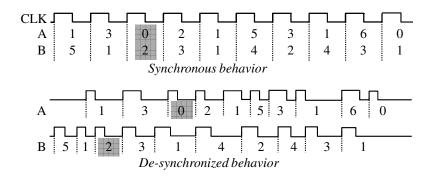

Synchronous flow

De-synchronized flow

Flow equivalence

[Guernic, Talpin, Lann, 2003]

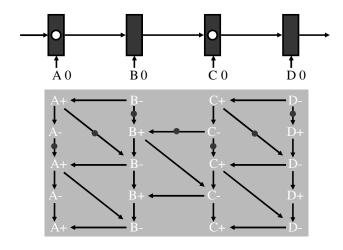

### Flow equivalence

### Flow equivalence

#### Outline

- What is de-synchronization?

- Behavioral equivalence

- 4-phase protocols for de-synchronization

- **■** Concurrency

- **■** Correctness

- An example

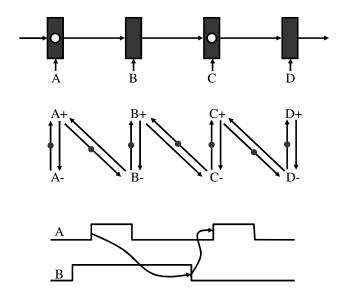

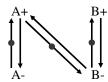

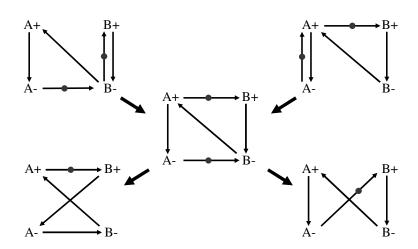

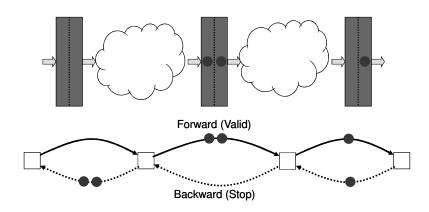

A latch cannot read another data item until the successor has captured the current one

A latch cannot become opaque before having captured the data item from its predecessor

### Outline

- What is de-synchronization?

- Behavioral equivalence

- 4-phase protocols for de-synchronization

- **■** Concurrency

- **■** Correctness

- An example

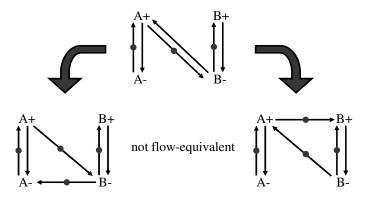

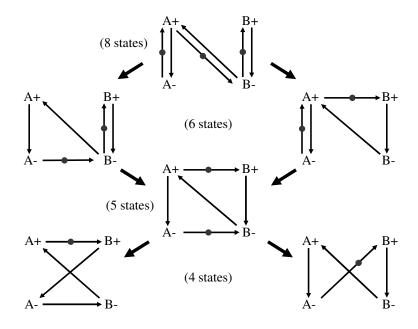

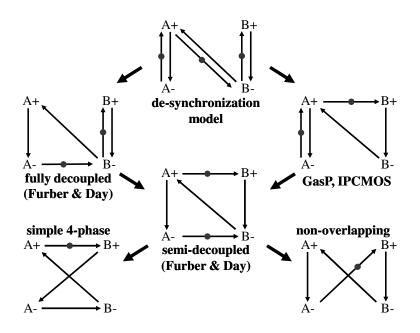

## Can we increase concurrency?

Can we reduce concurrency? How much?

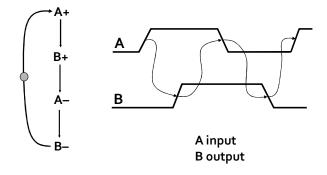

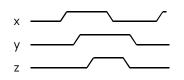

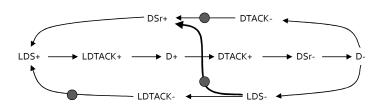

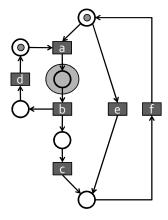

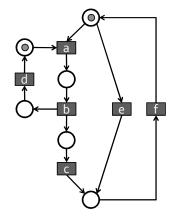

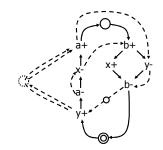

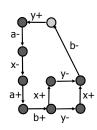

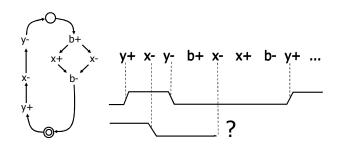

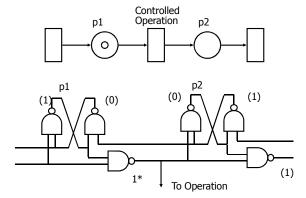

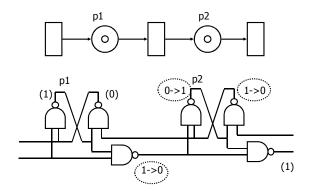

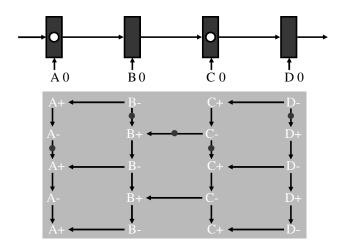

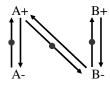

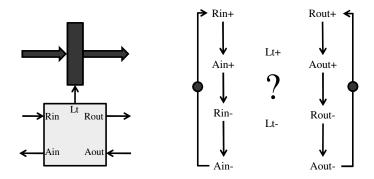

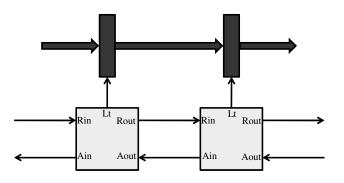

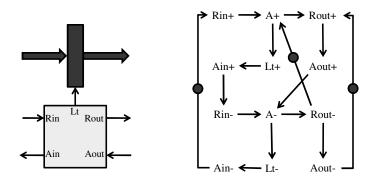

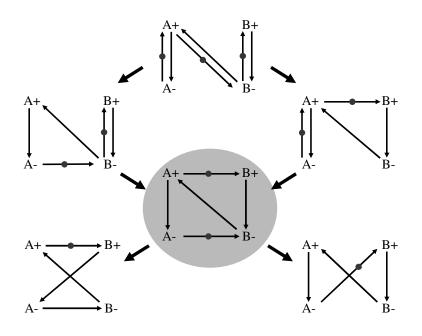

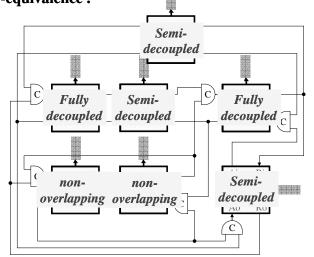

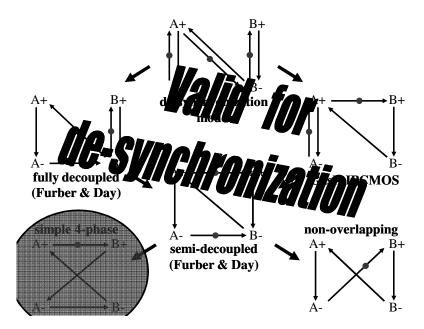

## 4-phase latch controllers

### 4-phase latch controllers

Furber and Day, IEEE Trans. VLSI, June 1996

Implementation note: Lt=0 (transparent), Lt=1 (opaque)

### 4-phase latch controllers

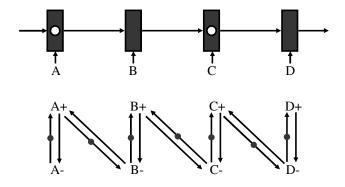

Simple 4-phase controller

### 4-phase latch controllers

Simple 4-phase controller

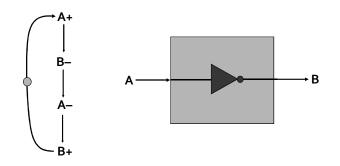

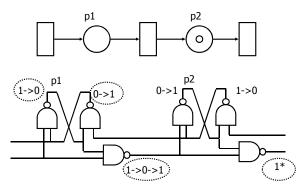

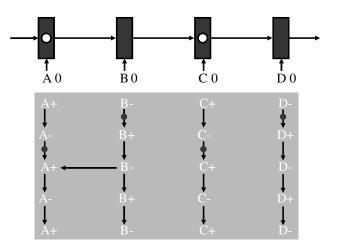

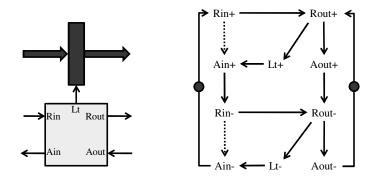

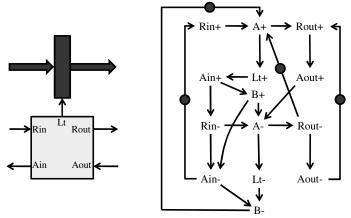

### 4-phase latch controllers

Semi-decoupled controller

### 4-phase latch controllers

Semi-decoupled controller

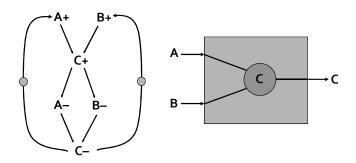

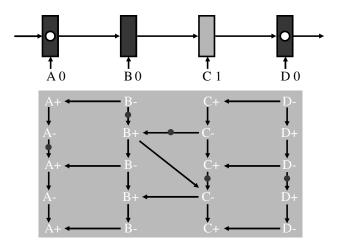

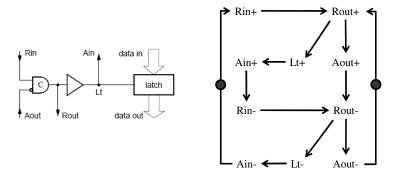

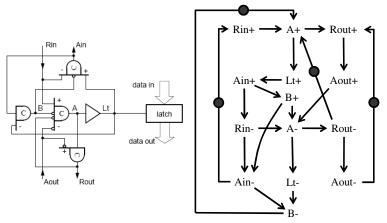

### 4-phase latch controllers

Fully decoupled controller

### 4-phase latch controllers

Fully decoupled controller

##

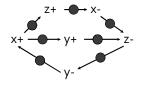

### 4-phase latch controllers (state graphs)

Semi-decoupled controller

Fully decoupled controller

(semi-decoupled 4-phase protocol)

#### Outline

- What is de-synchronization?

- Behavioral equivalence

- 4-phase protocols for de-synchronization

- **■** Concurrency

- **■** Correctness

- An example

#### Theorem:

the de-synchronization protocol preserves flow-equivalence

**<u>Proof:</u>** by induction on the length of the traces

Induction hypothesis: same latch values at reset Induction step:

same values at cycle  $i \rightarrow$  same values at cycle i+1

#### Theorem:

any reduction in concurrency preserves flow-equivalence

Flow-equivalence is preserved, ... but ...

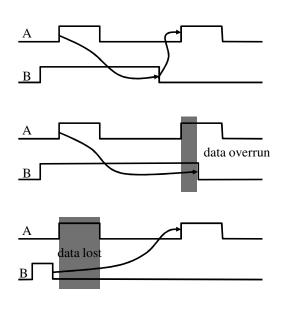

#### Liveness

- Preservation of flow-equivalence:

all the generated traces are equivalent

- Are all traces generated?

(Is the marked graph live?)

Not always!

Semi-decoupled 4-phase handshake protocol

Liveness: all cycles have at least one token [Commoner 1971]

Simple 4-phase handshake protocol

#### Results about liveness

- At least three latches in a ring are required with only one data token circulating [Muller 1962]

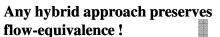

- <u>Theorem</u> (this paper): any hybrid combination of protocols is live if the simple 4-phase protocol is not used

**Proof:** any cycle has at least one token

#### Outline

- What is de-synchronization?

- Behavioral equivalence

- 4-phase protocols for de-synchronization

- Concurrency

- **■** Correctness

- *An example*

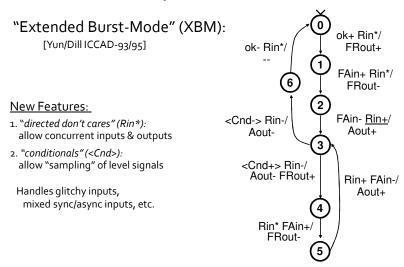

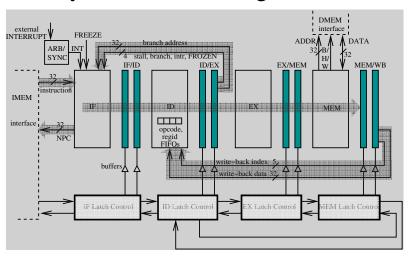

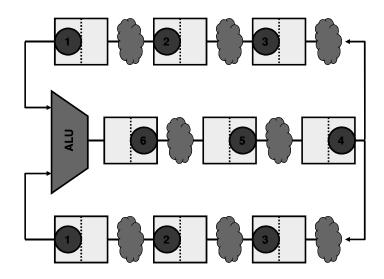

#### Async DLX block diagram

#### **Synchronous RTL**

- All numbers are after Placement & Routing

- Total of 1500 flip-flops, 3000 latches

- DE-SYNC design includes 5 controllers, each driving 2 clock trees

- Power numbers include the clock tree

- Technology: UCM/Virtual Silicon 0.18 µm

#### Discussion

■ The de-synchronization model provides an abstraction of the timing behavior

- Timing analysis

- Exploration of the design space

#### Conclusions

- EDA tools require a *formal support* (they must work for *all* circuits)

- A complete characterization of 4-phase protocols has been presented (partial order based on concurrency)

- Design flow developed at Cadence Berkeley Labs

- ◆ Automated from gate netlist

- ◆ Static timing analysis to derive matched delays

- ◆ Constrained P&R to meet timing constraints

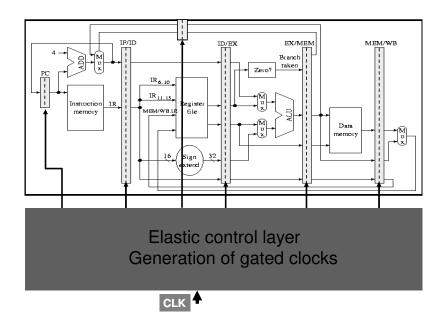

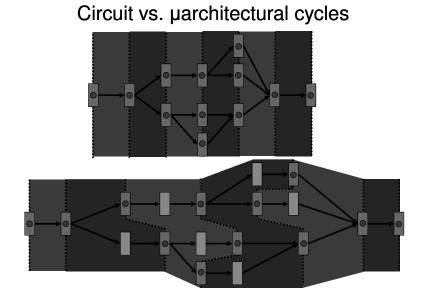

## Part 2: Synchronous Elastic Systems

Jordi Cortadella and Mike Kishinevsky

## Agenda of Part 2

- I. Basics of elastic systems

- II. Early evaluation and performance analysis

- III. Optimization of elastic systems and their correctness

- Synchronous elastic systems also called

- Latency tolerant systems or

- Latency insensitive systems

- We use term "synchronous elastic" since better linked to asynchronous elastic

ı

- What and Why

- Intuition

- How to design elastic systems

- Converting synchronous system to elastic

- Micro-arch opportunities

- Marked Graph models

- Performance evaluation

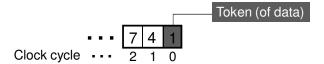

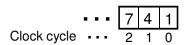

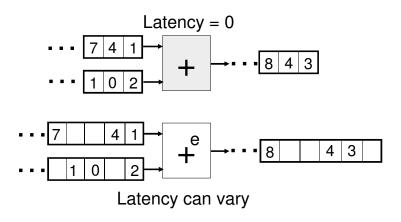

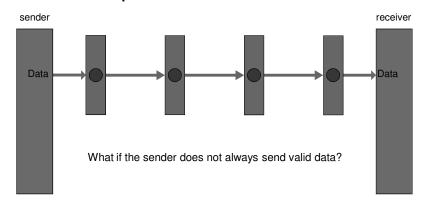

# Synchronous Stream of Data

# Synchronous Elastic Stream

# Synchronous Circuit

# Synchronous Elastic Circuit

## Ordinary Synchronous System

Changing latencies changes behavior

# Why

- Scalable

- Modular (Plug & Play)

- Better energy-delay trade-offs (design for typical case instead of worst case)

- New micro-architectural opportunities in digital design

- Not asynchronous: use existing design experience, CAD tools and flows

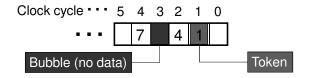

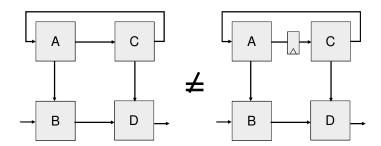

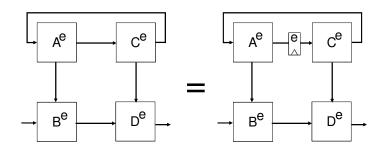

# Synchronous Elastic (characteristic property)

Changing latencies does NOT change behavior = time elasticity

# Example of elastic behavior

How to design elastic systems

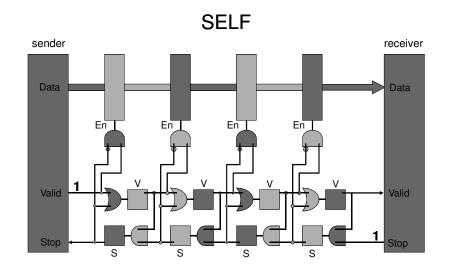

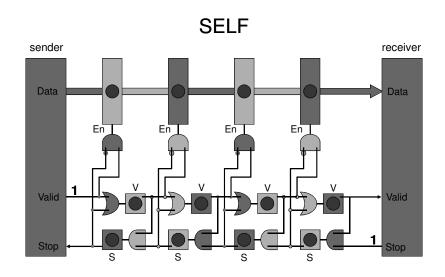

We show an example of the implementation: SELF = Synchronous Elastic Flow

Others are possible

# Reminder: Memory elements. Transparent latches

| Active high:                 | Active low:                  |  |  |  |

|------------------------------|------------------------------|--|--|--|

| En = o (opaque): Q = prev(Q) | En = 1 (opaque): Q = prev(Q) |  |  |  |

| En = 1 (transparent): Q = D  | En = o (transparent): Q = D  |  |  |  |

16

Reminder: Memory elements. Flip-flop

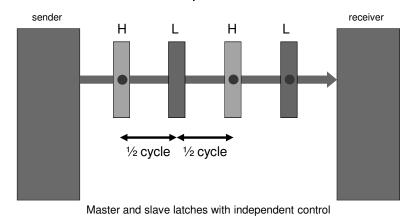

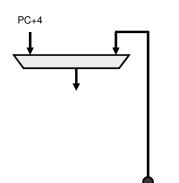

# Reminder: Clock cycle = two phases

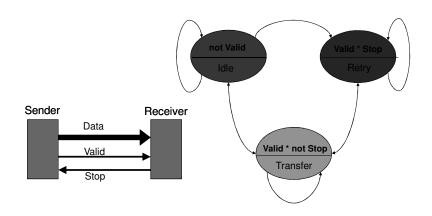

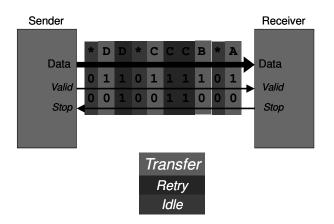

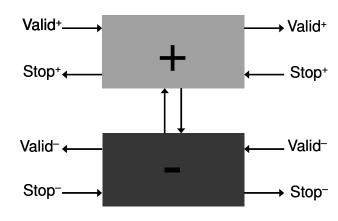

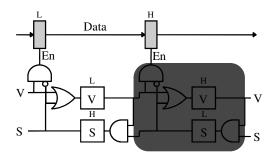

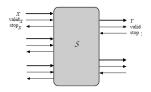

# Elastic channel protocol

# Elastic channel protocol

#### Elastic buffer keeps data while stop is in flight

#### Communication channel

# Pipelined communication

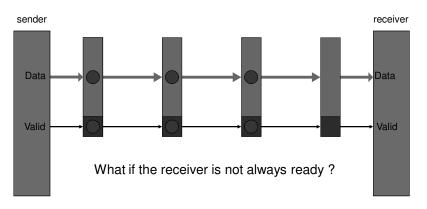

#### The Valid bit

# The Stop bit sender receiver Data Valid Stop 1 1 Stop Back-pressure

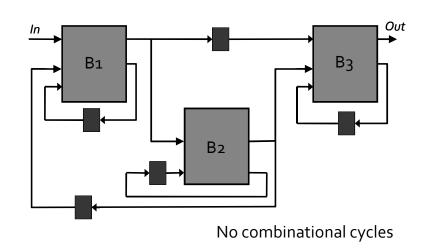

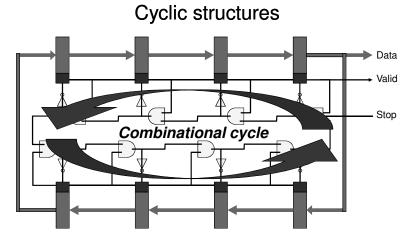

One can build circuits with combinational cycles (constructive cycles by Berry), but synthesis and timing tools do not like them

# Example: pipelined linear communication chain with transparent latches

# Shorthand notation (clock lines not shown)

# SELF (linear communication) sender Data Para Language Stop Sto

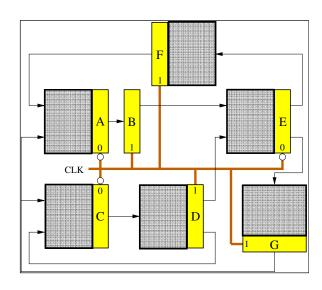

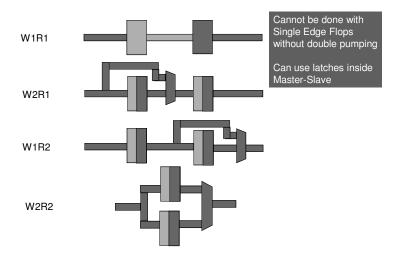

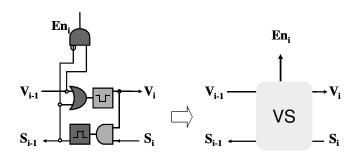

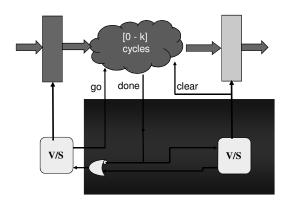

#### Basic VS block

VS block + data-path latch = elastic HALF-buffer

# Variable Latency Units (to be changed)

# Elasticization

Micro-architectural opportunities

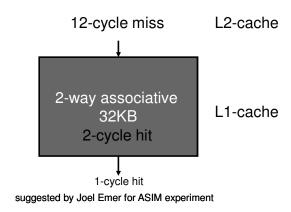

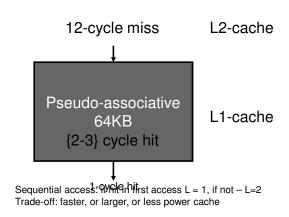

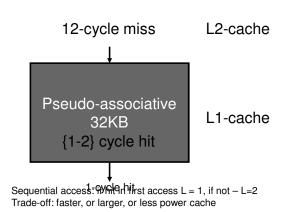

## Variable-latency cache hits

# Variable-latency cache hits

#### Variable-latency cache hits

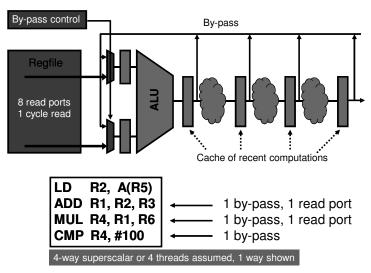

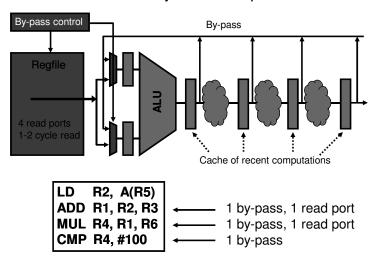

#### Variable-latency RF with less ports

#### Variable-latency RF with less ports

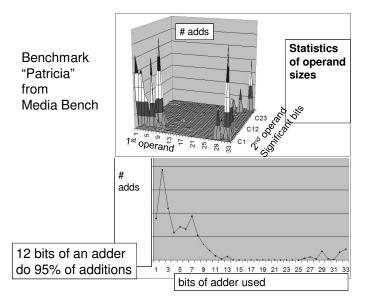

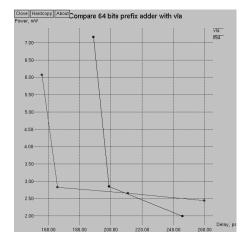

## Variable-latency ALUs

- In most of the ADD/SUB operations, only few LSBs are used. The rest are merely for sign extension.

- Use the idea of telescopic units:

- 1-cycle addition for 16 bits and sign extension

- 2 or more cycles for 64-bit additions (rare case)

- maybe there is no need for CLA adders ...

- or do all additions with 16-bit adders only

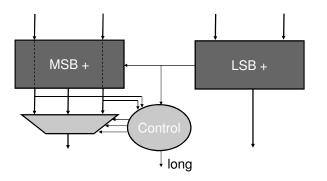

#### Variable Latency Adder

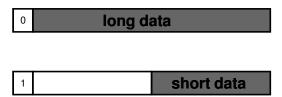

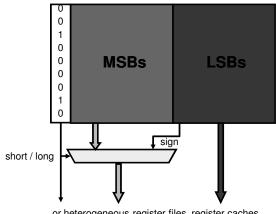

# Power-delay [preliminary]

Pre-compute and tag size information

... and select functional unit according to the size of the data

# Partitioned register file

or heterogeneous register files, register caches

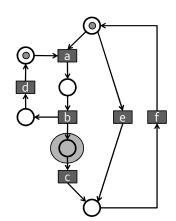

Reminder: Petri Nets and Marked Graphs

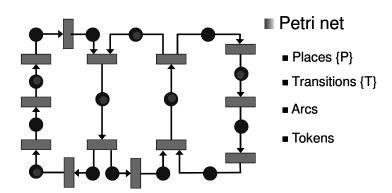

#### Petri nets

## Petri nets. Token game

#### **Enabling Rule:**

- A transition is enabled if all its input places are marked

- Enabled transition can fire at any time

#### Firing Rule:

- One token is removed from every input place

- One token is added to every output place

- Change of marking is atomic

#### Petri nets. Token game

#### **Enabling Rule:**

- A transition is enabled if all its input places are marked

- Enabled transition can fire at any time

#### Firing Rule:

- One token is removed from every input place

- One token is added to every output place

- Change of marking is atomic

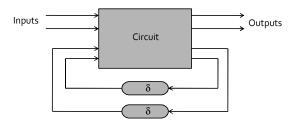

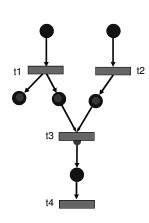

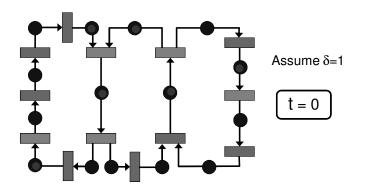

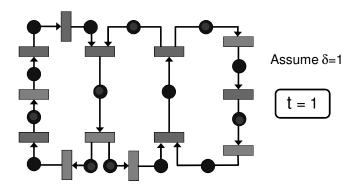

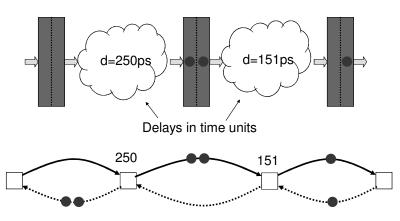

#### **Timed Petri nets**

- $\blacksquare$  Assign a delay ( $\delta$ ) to every transition

- An enabled transition fires  $\delta$  time units after enabling

#### **Timed Petri nets**

- $\blacksquare$  Assign a delay ( $\delta$ ) to every transition

- An enabled transition fires  $\delta$  time units after enabling

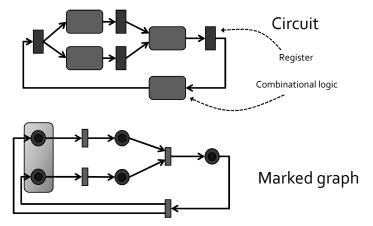

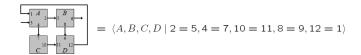

Marked Graph models of elastic systems

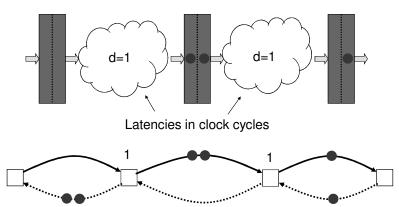

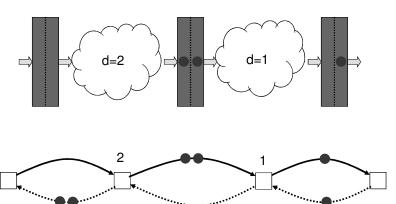

#### **Timed Petri nets**

- Assign a delay ( $\delta$ ) to every transition

- $-\,$  A transition with marked input places will fire after  $\delta$  time units

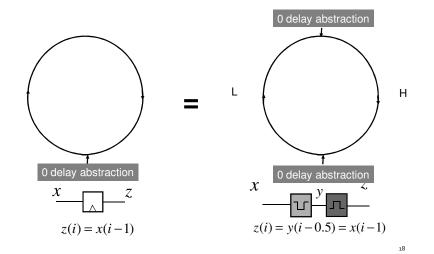

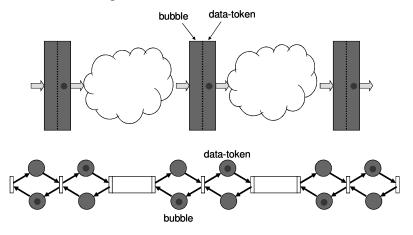

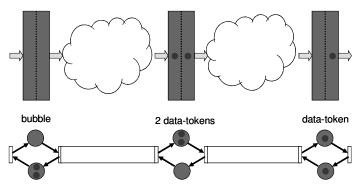

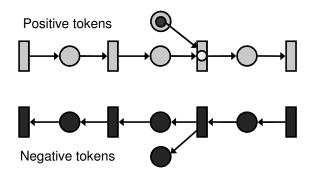

# Modelling elastic control with Petri nets

# Modelling elastic control with Petri nets

Hiding internal transitions of elastic buffers

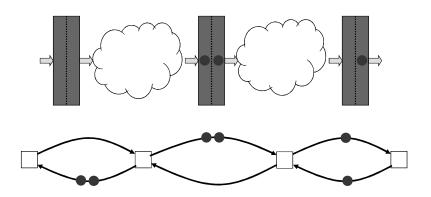

#### Modelling elastic control with Marked Graphs

#### Modelling elastic control with Marked Graphs

# Elastic control with Timed Marked Graphs. Continuous time = asynchronous

# Elastic control with Timed Marked Graphs. Discrete time = synchronous elastic

# Elastic control with Timed Marked Graphs. Discrete time. Multi-cycle operation

# Elastic control with Timed Marked Graphs. Discrete time. Variable latency operation

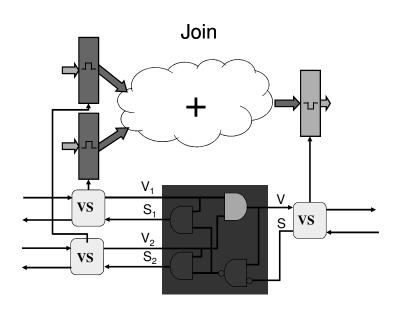

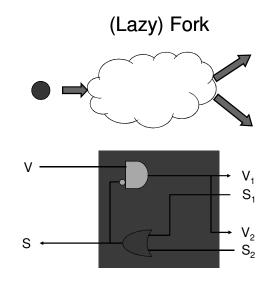

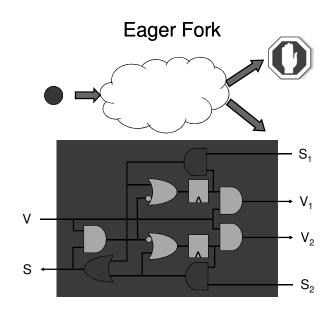

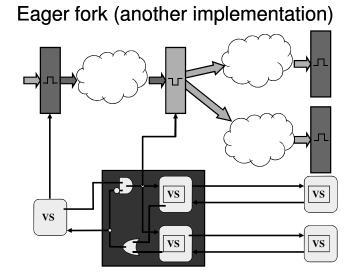

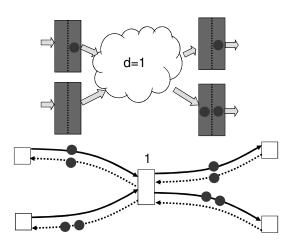

# Modeling forks and joins

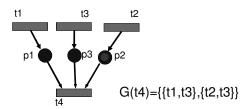

# Elastic Marked Graphs

■ An Elastic Marked Graph (EMG) is a Timed MG such that for any arc *a* there exists a complementary arc *a'* satisfying the following condition

•a = a'• and •a' = a•

- Initial number of tokens on a and a' (Mo(a)+Mo(a')) = capacity of the corresponding elastic buffer

- Similar forms of "pipelined" Petri Nets and Marked Graphs have been previously used for modeling pipelining in HW and SW (e.g. Patil 1974; Tsirlin, Rosenblum 1982)

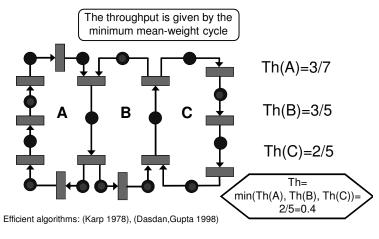

#### Performance analysis on Marked Graphs

# Performance Th = operations / cycle

# Performance Th = 3/7

# Performance

Th = 3/5

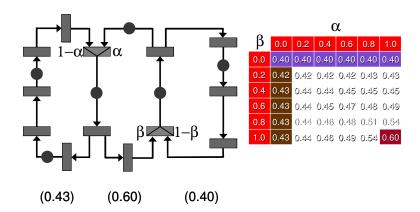

# Performance

Th = min(0.43, 0.6, 0.4)

# Performance

Th = 2/5

# Performance

$Th = min(0.43, 0.6, \underline{0.4})$

Ш

- Early evaluation

- Dual Marked Graphs

- Implementing early evaluation

- Performance analysis

#### Examples of early evaluation

#### Goal: Improve system performance and power

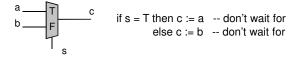

#### MULTIPLIER

if a = 0 then c := 0 -- don't wait for b

#### **MULTIPLEXOR**

## Early evaluation

- Naïve solution: introduce choice places

- issue tokens at choice node only into one (some) relevant path

- problem: tokens can arrive to merge nodes out-of-order later token can overpass the earlier one

- Solution: change enabling rule

- early evaluation

- issue negative tokens to input places without tokens, i.e. keep the same firing rule

- Add symmetric sub-channels with negative tokens

- Negative tokens kill positive tokens when meet

- Two related problems: Early evaluation and Exceptions (how to kill a data-token)

# Example: next-PC calculation

Branch target address

#### Related work

- Petri nets

- Extensions to model OR causality

[Kishinevsky et al. 1994, Yakovlev et al. 1996]

- Asynchronous systems

- Reese et al 2002: Early evaluation

- Brej 2003: Early evaluation with anti-tokens

- Ampalan & Singh 2006: preemption using anti-tokens

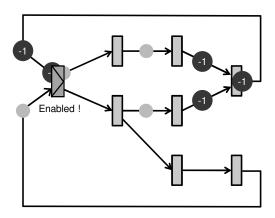

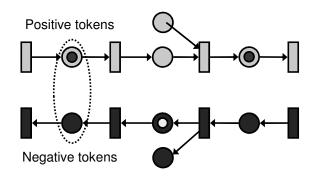

#### **Dual Marked Graph**

- Marking: Arcs (places) -> Z

- Some nodes are labeled as early-enabling

- Enabling rules for a node:

- Positive enabling: M(a) > 0 for every input arc

- Early enabling (for early enabling nodes): M(a) > 0 for some input arcs

- Negative enabling: M(a) < 0 for every output arc

- Firing rule: the same as in regular MG

#### **Dual Marked Graphs**

#### **Dual Marked Graphs**

- Early enabling is only defined for nodes labeled as earlyenabled. Models computations that can start before all the incoming data available

- Early enabling can be associated with an external guard that depends on data variables (e.g., a select signal of a multiplexor)

- In DMG actual enabling guards are abstracted away

- Anti-token generation: When an early enabled node fires, it generates anti-tokens in the predecessor arcs that had no tokens

- Anti-token propagation counterflow: When negative enabled node fires, it propagates the anti-tokens from the successor to the predecessor arcs

#### **Dual Marked Graph model**

#### Passive anti-token

- Passive DMG = version of DMG without negative enabling

- Negative tokens can only be generated due to early enabling, but cannot propagate

- Let D be a DMG and  $D_p$  be a corresponding passive DMG. If environment (consumers) never generate negative tokens, then throughput (D) = throughput  $(D_p)$

- If capacity of input places for early enabling transitions is unlimited, then active anti-tokens do not improve performance

- Active anti-tokens reduce activity in the data-path (good for power reduction)

## **Properties of DMGs**

- Firing invariant: Let node *n* be simultaneously positive (or early) and negative enabled in marking *M*. Let M1 be the result of firing *n* from *M* due to positive (or early) enabling. Let M2 be the result of firing *n* from *M* due to negative enabling. Then, M1 = M2.

- Token preservation. Let c be a cycle of a strongly connected DMG. For every reachable marking M, M(c) = Mo(c).

- <u>Liveness</u>. A strongly connected DMG is live iff for every cycle c: M(c) > 0.

- Repetitive behavior. In a SC DMG: a firing sequence s from M leads to the same marking iff every node fires in s the same number of times.

- DMGs have properties similar to regular MGs

Implementing early enabling

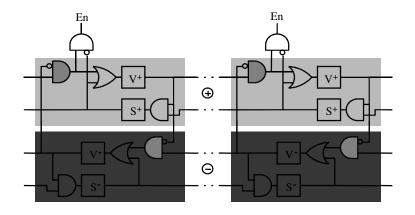

# How to implement anti-tokens?

# How to implement anti-tokens?

# How to implement anti-tokens?

# Controller for elastic buffer

#### Dual controller for elastic buffer

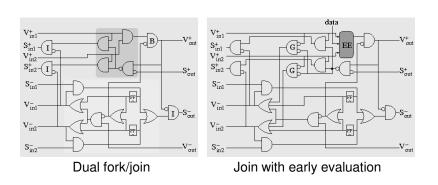

# Dual fork/join and early join

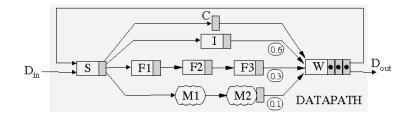

# Example

| Evaluation                 | Throughput |

|----------------------------|------------|

| No early evaluation        | 0.277      |

| Passive anti-tokens M2 → W | 0.280      |

| Passive anti-tokens F3 → W | 0.387      |

| Active anti-tokens         | 0.400      |

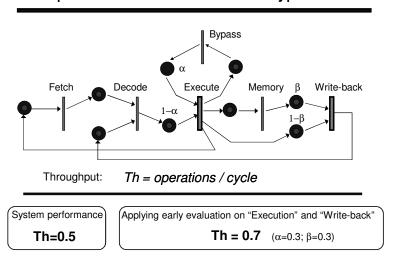

#### DLX processor model with slow bypass

#### Conclusions

- Early evaluation can increase performance beyond the min cycle ratio

- The duality between tokens and anti-tokens suggests a clean and effective implementation

# Performance analysis with early evaluation

(joint work with Jorge Júlvez)

# Reminder: Performance analysis of Marked graphs

Th = operations / cycle = number of firings per time unit

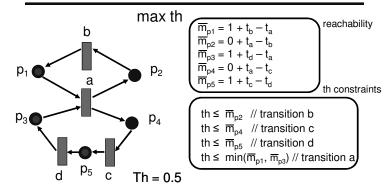

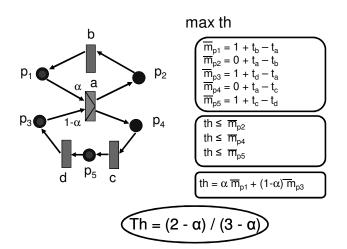

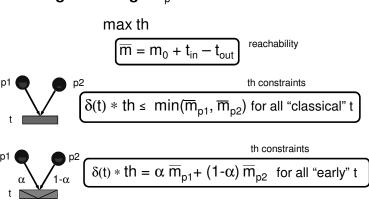

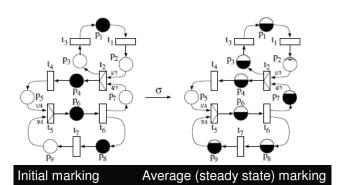

#### Marked graphs. Performance analysis

The throughput can also be computed by means of linear programming

$$th = \min(\overline{m}_{p1}, \overline{m}_{p2})$$

Average marking

$$\overline{m}_p = \lim_{t \to \infty} \frac{1}{t} \int_0^t m_p(\tau) d\tau$$

Throughput

$$th = \min_{p} \overline{m}_{p}$$

#### Marked graphs. Performance analysis

The throughput can also be computed by means of linear programming

$$th = \min_{p} \overline{m}_{p}$$

[Campos, Chiola, Silva 1991]

## Multi-guarded Dual Marked Graph

#### Execution of transitions:

- At the initial marking and each time t fires one of guards gi from G(t) is non-deterministically selected

- Selection is persistent (cannot change between firings of t)

Accurate non-deterministic abstraction of the early

- Accurate non-deterministic abstraction of the early evaluation conditions (e.g. multiplexor select signals)

- t is enabled when for every place p in selected gi: M(p) > 0

- enabled t can fire (regular firing rule)

- Single-server semantics: no multiple-instances of the same transition can fire simultaneously

- Abstraction for systems that communicate through FIFO channels

#### GMG = Multi-guarded Dual Marked Graph

- Refinement of passive DMGs

- Every node has a set of guards

- Every guard is a set of input arcs (places)

- Simple transition has one guard with all input places

#### Example:

#### **Timed GMG**

- Every transition is assigned a non-negative delay  $\delta(t)$   $\delta(t)$ =1 unless specified otherwise

- Every guard g of every guarded transition is assigned a strictly positive probability p(g) such that for every t:

$$\sum_{g \in G(t)} p(g) = 1$$

- Guard selection for every transition is non-deterministic, but respects probabilities in the infinite executions

- Probabilities assumed to be independent (generous abstraction)

- Firing of transition t takes  $\delta(t)$  time units, from the time it becomes enabled until the firing is completed

#### Early evaluation

#### **Timed GMG**

{Places, Transitions,  $\delta$ , Prob}

Throughput?

Marked graphs with early evaluation

stochastic dynamic system

Alternatives to compute the throughput:

- Simulation

- Markov chain

- Linear programming

#### Early evaluation

## Throughput

$$Th = \lim_{\tau \to \infty} \sigma(\tau)/\tau$$

- $\tau$  time,  $\sigma(\tau)$  firing vector

- This limit exists for every timed GMG

- It is the same for all transitions!

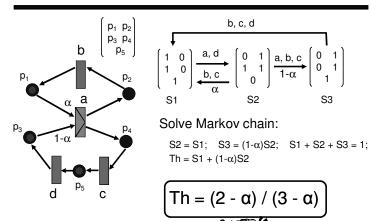

#### Markov chains

# State explosion problem!

#### Linear programming. Example

#### Linear programming formulation

#### Average marking: $\overline{m}_p$

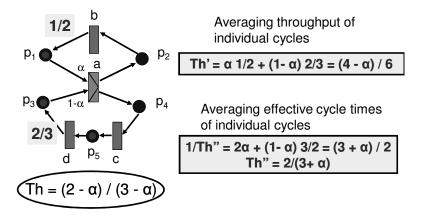

# Averaging cycle throughput or cycle times does not work

# Example

## Linear programming

In general the LP yields a throughput upper bound

Particular cases of exact throughput:

- No early joins (i.e. MGs)

- · All joins are early evaluation

#### Throughput estimation

- Throughput estimation:

- 1. Up = throughput obtained with LP

- 2. Low = throughput without early enabling

- 3. Th = (Up + Low)/2

#### Results

Circuits from MCNC

2-input gates

a latch for each gate

75% tokens, 25% bubbles

25% muxes

Random select probability

| Name  | Nodes | Edges | MG=Low | Real  | Up    | ΔTh  | Err |

|-------|-------|-------|--------|-------|-------|------|-----|

| s27   |       |       | 0.333  | 0.333 | 0.333 | 0 %  |     |

| S208  |       |       | 0.500  | 0.571 | 0.594 | 14 % |     |

| s298  |       |       | 0.091  | 0.120 | 0.129 | 32 % |     |

| s349  |       |       | 0.333  | 0.333 | 0.333 | 0 %  |     |

| s382  |       |       | 0.250  | 0.284 | 0.294 | 14 % |     |

| s386  |       |       | 0.400  | 0.400 | 0.400 | 0 %  |     |

| s400  |       |       | 0.400  | 0.438 | 0.470 | 10 % |     |

| S444  |       |       | 0.200  | 0.261 | 0.287 | 31 % |     |

| S510  |       |       | 0.167  | 0.167 | 0.167 | 0 %  |     |

| S526  |       |       | 0.333  | 0.333 | 0.333 | 0 %  |     |

| S641  |       |       | 0.333  | 0.393 | 0.432 | 18 % |     |

| S713  |       |       | 0.250  | 0.333 | 0.333 | 33 % |     |

| S820  |       |       | 0.143  | 0.201 | 0.230 | 41 % |     |

| S832  |       |       | 0.286  | 0.310 | 0.342 | 8 %  |     |

| S953  |       |       | 0.286  | 0.295 | 0.333 | 3 %  |     |

| S1423 |       |       | 0.100  | 0.184 | 0.189 | 84 % |     |

| S1488 |       |       | 0.188  | 0.236 | 0.271 | 26 % |     |

| S1494 |       |       | 0.154  | 0.222 | 0.277 | 44 % |     |

| S5378 |       |       | 0.235  | 0.250 | 0.250 | 6 %  |     |

| s9234 |       |       | 0.200  | 0.219 | 0.248 | 10 % |     |

#### Summary

- Early evaluation to improve system throughput

- Evaluate expressions as soon as possible

- Generate antitokens to erase "don't care" bits

- Analytical model to estimate the throughput

- Useful for architectural exploration

- Which muxes must have early evaluation?

- Where do we put our by-passes ?

- Faster than simulation

- Simulation can be used at later design stages

# **Buffer sizing**

(joint work with Dmitry Bufistov)

#### Ш

- Optimization

- Slack matching and buffer sizing

- Retiming and recycling

- Clustering controllers

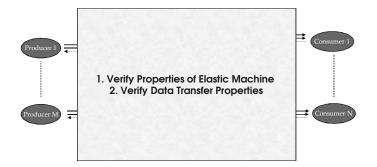

#### Correctness

- Theory of elastic machines

- Formal verification

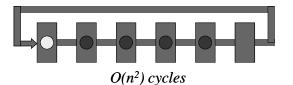

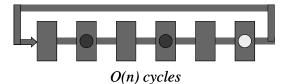

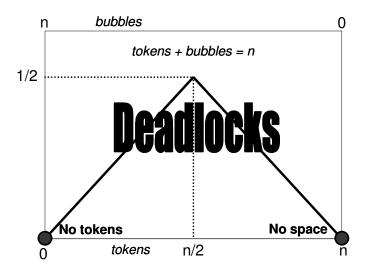

#### How many bubbles do we need?

#### Throughput of an *n*-stage ring

#### Optimization techniques

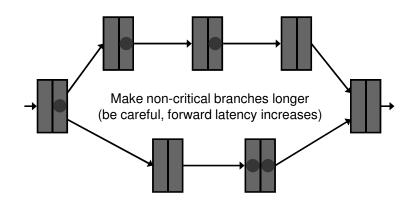

- Buffer sizing: select optimal capacity of elastic buffers without increasing forward latency for propagating data-tokens

- Slack matching: insert additional empty elastic buffers

- increases buffer capacity

- but, typically increases forward latency as well

- also called recycling in the context of synchronous elastic (latency-tolerant) designs

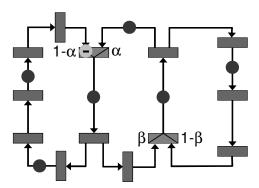

## What flexibility do we have?

- Number of tokens on a loop cannot be easily changed (inherent to the computation)

- Bubbles can always be added (as many as necessary), but may decrease throughput

- Buffer sizes can always be increased (provided forward latency of the buffer does not change)

- Tokens determine the maximum achievable throughput (assuming infinite buffer sizes)

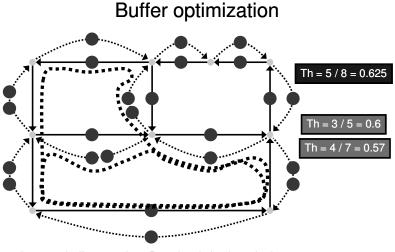

#### **Buffer optimization**

# **Buffer optimization**

# **Buffer optimization**

Why?

Solution 1: slack matching/recycling

Solution 2: increase buffer size

#### Slack matching vs. buffer capacity

- Not equivalent (slack matching cannot always achieve the forward latency, while buffer capacity can)

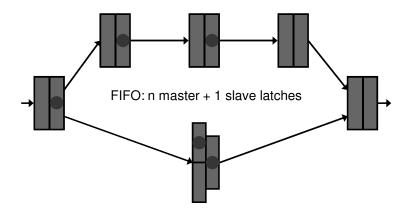

- Slack matching is a well-studied problem in asynchronous design

- Slack matching = inc buffer capacity + split

#### Increase buffer capacity = Put token in backward edge

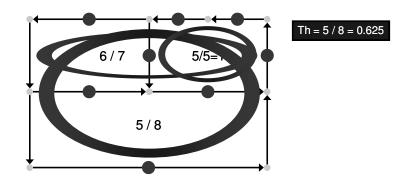

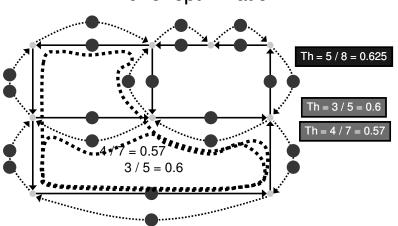

# Buffer optimization Th = 5/8 = 0.625Th = 4/7 = 0.57

Increase buffer capacity = Put token in backward edge

## **Buffer sizing**

- Find min possible increase in buffer sizes such that the throughput is equal to the throughput of a system with infinite size buffers

- Combinatorial problem

- We found an exact ILP formulation, but ...

- ILP is exponential

- Can we do better (polynomial time) ?

## LP performance model

#### Buffer sizing is NP-complete

- NP-hardness: reduction of "min edges that cut all cycles in a digraph" to buffer sizing

- NP: Checking validity of solution can be done in polynomial time (e.g. Karp's algorithm)

- Therefore,

No polynomial algorithm exists, unless P = NP

#### ILP model for buffer sizing

#### Table of results

| Circuit | IVI  | IEI   | Th   | Max<br>Th | ΔTok | CPU (sec) | Mem<br>(Mb) |

|---------|------|-------|------|-----------|------|-----------|-------------|

| s1423   | 484  | 942   | 0.33 | 0.33      | 0    | <1        | 81          |

| s1488   | 321  | 1662  | 0.5  | 0.5       | 0    | <1        | 95          |

| s1494   | 341  | 1775  | 0.5  | 0.5       | 0    | 1         | 108         |

| s208    | 36   | 100   | 0.5  | 1         | 26   | 1         | 1           |

| s27     | 31   | 78    | 0.5  | 0.75      | 18   | <1        | 1           |

| s298    | 823  | 7154  | 0.5  | 0.5       | 0    | 5         | 946         |

| s349    | 139  | 241   | 0.5  | 0.6       | 3    | <1        | 7           |

| s386    | 86   | 339   | 0.5  | 0.5       | 0    | <1        | 7           |

| s400    | 119  | 273   | 0.33 | 0.33      | 0    | <1        | 7           |

| s444    | 132  | 298   | 0.33 | 0.33      | 0    | <1        | 8           |

| s510    | 149  | 571   | 0.5  | 0.5       | 0    | <1        | 16          |

| s526    | 145  | 382   | 0.33 | 0.33      | 0    | <1        | 11          |

| s5378   | 1138 | 2484  | 0.42 | 0.55      | 30   | 4708      | 500         |

| s641    | 182  | 298   | 0.5  | 0.67      | 6    | <1        | 11          |

| s713    | 208  | 350   | 0.42 | 0.5       | 1    | <1        | 15          |

| s820    | 183  | 919   | 0.5  | 0.5       | 0    | <1        | 31          |

| s832    | 191  | 972   | 0.5  | 0.5       | 0    | <1        | 34          |

| s9234   | 1023 | 1992  | 0.25 | 0.25      | 0    | <1        | 350         |

| s953    | 373  | 704   | 0.45 | 0.64      | 10*  | >21600    | 60          |

| s38417  | 8315 | 16440 | 0.25 | 0.33      | -    | -         | >2Gb        |

\* - Non optimal integral solution with time limit 120 seconds

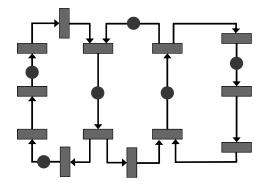

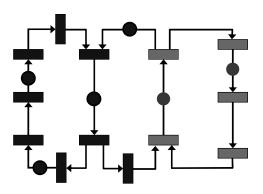

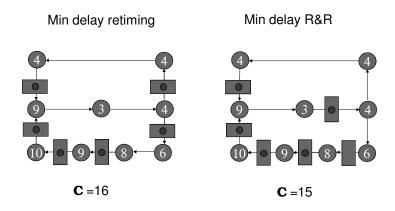

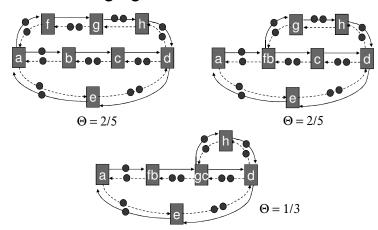

# Retiming and Recycling

(joint work with Dmitry Bufistov and Sachin Sapatnekar)

# Retiming

- Retiming: moving registers across combinational blocks or (equivalently) moving combinational blocks across registers

n retimed backward

- forward retiming

- backward retiming

n retimed forward

- Retiming in elastic systems

- all registers participating in the retiming move should be labeled with the same number of data-tokens

- use of negative tokens can remove the above constraint (will not discuss here)

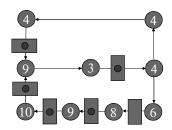

#### Recycling

- Recycling: insert (or remove) empty elastic buffers (empty registers for short) on any edge

- possible only in elastic systems

- We will ignore initialization and consider only steady state behavior

- Initialization to an equivalent state almost always possible, but may require extra logic

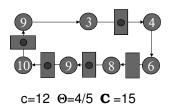

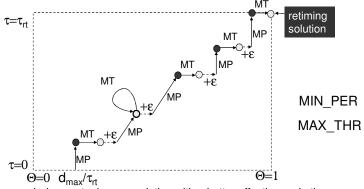

## **Effective Cycle Time**

- Cycle time: c = max {path delay between registers}

- Throughput:  $\Theta = \min \{ \text{tokens/cycle} \}$  Was formally defined before

- Effective cycle:  $\mathbf{C} = \mathbf{c} / \Theta$

## R&R is more powerful than retiming

## R&R graph (RRG)

- combinational block with a delay of 10 units

- register (EB) with one data token

- empty register (EB with no data tokens)

## Analogy between circuit retiming and reachability in MGs

- Retiming graph of a circuit = MG:

- combinational block = node

- connection = edge

- register = token

- firing rules = backward retiming rules: each time a node is retimed, registers are removed from the input edges and added to the output edges

- MGs: A live marking M of an SCMG is reachable iff  $M(\phi) = M0(\phi)$  for every cycle  $\phi$ .

Retiming interpretation.

- => valid retiming preserves the number of registers at each cycle

- <= if an assignment of registers has the same number of registers at each cycle as the initial circuit, then the assignment is a valid retiming.

# Analogy between circuit retiming and reachability in MGs

■ Non-negative marking M is reachable iff the marking equation holds:

$$M = M0 + A \times \sigma$$

■ Retiming interpretation:

■ M0 - initial assignment of registers to edges

■ M -assignment after retiming

■ A - retiming matrix

■ σ – retiming vector

■ Rename M to R:  $R = R0 + A \times \sigma$

■ ILP formulation (A is totally unimodular. Polynomial problem)

#### Valid R&R solutions

Any integer solution for R and R':

$$R > R' = R_0 + A \times \sigma$$

is a valid R&R solution

■ R' retiming subset (registers with data-tokens)

R represents the R&R solution (registers with data-tokens or bubbles)

■ (R – R') registers with bubbles (recycling)

## Example of marking equation

## Combinational path constraints

$$tin(e) \ge tout(e') + \delta(u), \forall e' = (w, u)$$

$tout(e) \ge tin(e) - \tau' \times R(e)$

$tout \ge 0$

$tin(e) \le \tau$

$\tau$  – desired cycle time

$\tau'$  – original cycle time or any other constant >  $\tau$

$\delta(u)$  – node u delay

R(e) – number of register on edge e=(u,v)

Register delays can be taken into account

## Throughput constraints

$$R \le (R_0 + A \times \sigma)/\Theta$$

Let R be a valid R&R register assignment. There is a nonnegative real vector  $\sigma$  that fulfils the above inequality iff  $\Theta(R) > \Theta$

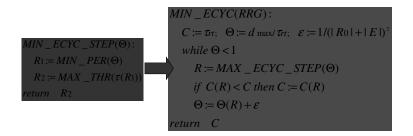

## Min period R&R

Given an RRG and a throughput  $\Theta > 0$ , find a register assignment R that minimizes the cycle time  $\tau$  and has throughput  $\Theta(R) \Rightarrow \Theta$ .

$$MIN\_PER(\Theta) = \begin{cases} \min \tau \\ subject & to \quad RR(\tau, \Theta) \end{cases}$$

#### ILP formulation for R&R

$$RR(\tau, \Theta) = \begin{cases} R \ge R0 + A \times \sigma 1 \ge 0 \\ R \le (R0 + A \times \sigma 2) / \Theta \\ Path\_constr(R, \tau) \\ R, \sigma 1 \in \text{int} \end{cases}$$

Given a cycle time  $\,\tau$  and a throughput  $\,\Theta$ , R is a valid R&R register assignment of an RRG (N,E,R0,  $\delta$ ) with  $\tau(R) < \tau$  and  $\Theta(R) > \Theta$  iff there exists a feasible solution of the above ILP

## Max throughput R&R

Given an RRG and a cycle period  $\tau$ , find a register assignment R with  $\tau(R) <= \tau$  that maximizes the throughput  $\Theta(R)$ .

$$MAX\_THR\_NL(\tau) = \begin{cases} \max \Theta \\ subject & to & RR(\tau, \Theta) \end{cases}$$

This problem is not linear (and not convex):  $\Theta$  is a variable of the model and the second constraint of  $RR(\tau, \Theta)$  is not linear.

Use binary search on different  $\Theta$

## Size of the interval for binary search