# RELATIVE TIMING BASED VERIFICATION OF CONCURRENT SYSTEMS

# MARCO ANTONIO PEÑA BASURTO

Llicenciat en Informàtica, Technical University of Catalonia, Barcelona, Spain 1993 Llicenciat amb grau en Informàtica, Technical University of Catalonia, Barcelona, Spain 1995

Department of Computer Architecture Technical University of Catalonia Barcelona (Spain), February, 2003

A thesis submitted in partial fulfillment of the requirements for the degree of Doctor en Informàtica

Para mi no hay emoción comparable a la que produce la actividad creadora, tanto en ciencia como en arte, literatura u otras ocupaciones del intelecto humano. Mi mensaje, dirigido sobre todo a la juventud, es que si sienten inclinación por la ciencia, la sigan, pues no dejará de proporcionarles satisfacciones inigualables. Cierto es que abundan los momentos de desaliento y frustración, pero éstos se olvidan pronto, mientras que las satisfacciones no se olvidan jamás.

—Severo Ochoa

It has long been my personal view that the separation of practical and theoretical work is artificial and injurious. Much of the practical work done in computing, both in software and hardware design, is unsound and clumsy because the people who do it do not have any clear understanding of the fundamental principles underlying their work. Most of the abstract mathematics and theoretical work is sterile because it has no contact with the real computing.

—Christopher Strachey

# CONTENTS

| LIST  | OF FIGURES                                   | xi   |

|-------|----------------------------------------------|------|

| LIST  | OF TABLES                                    | xv   |

| ABST  | TRACT                                        | xvii |

| ACKI  | NOWLEDGMENTS                                 | xix  |

| 1 IN' | TRODUCTION                                   | 1    |

| 1.1   | Introduction                                 | 2    |

| 1.2   | 2 Formal methods                             | 3    |

|       | 1.2.1 Formal methods in the design process   | 4    |

| 1.3   | Formal verification                          | 6    |

|       | 1.3.1 Verification versus simulation         | 7    |

|       | 1.3.2 Main approaches to formal verification | 8    |

| 1.4   | Formal verification of timed systems         | 10   |

| 1.5   | 6 Overview of the contributions              | 11   |

| 1.6   | Structure of the thesis                      | 14   |

| 2 M(  | ODELS FOR CONCURRENT SYSTEMS                 | 17   |

| 2.1   | Introduction                                 | 18   |

| 2.2   | 2 Transition systems                         | 18   |

| 2.3   | Timed transition systems                     | 21   |

| 2.4   | Lazy transition systems                      | 24   |

| 2.5   | 6 Petri nets                                 | 27   |

|       | 2.5.1 Labeled Petri nets                     | 31   |

| 2.6   | 6 Conclusions                                | 33   |

| 3 VE  | CRIFICATION OF TIMED SYSTEMS                 | 35   |

| 3.1   | Introduction                                 | 36   |

| 3.2   | 2 Quantitative timing information            | 37   |

| 3.3   | Timed automata                               | 39   |

| 3.4   | Timed specifications                         | 42   |

|       | 3.4.1 Temporal logic                         | 42   |

|       | 3.4.2 Timed temporal logic                   | 45   |

VIII CONTENTS

|   | 3.5 | Verification of timed systems                                             | 46  |

|---|-----|---------------------------------------------------------------------------|-----|

|   |     | 3.5.1 Clock regions                                                       | 46  |

|   |     | 3.5.2 Region automata                                                     | 48  |

|   |     | 3.5.3 Zone automata                                                       | 48  |

|   |     | 3.5.4 Difference-bound matrices                                           | 49  |

|   |     | 3.5.5 Discussion                                                          | 50  |

|   | 3.6 | Petri net-based methods                                                   | 51  |

|   | 3.7 | Conclusions                                                               | 52  |

| 4 | VEF | RIFICATION WITH RELATIVE TIMING                                           | 53  |

|   | 4.1 | Introduction                                                              | 54  |

|   |     | 4.1.1 Relative Timing                                                     | 55  |

|   | 4.2 | Overview                                                                  | 57  |

|   | 4.3 | Trace semantics                                                           | 62  |

|   |     | 4.3.1 Traces and languages                                                | 62  |

|   |     | 4.3.2 Trace-based verification                                            | 63  |

|   |     | 4.3.3 Enabling compatibility                                              | 66  |

|   | 4.4 | Event structures                                                          | 70  |

|   |     | 4.4.1 Timing analysis on event structures                                 | 74  |

|   | 4.5 | Enabling-compatible product                                               | 77  |

|   |     | 4.5.1 State-based representation of a CES                                 | 77  |

|   |     | 4.5.2 Refining the reachability space by timing constraints               | 79  |

|   | 4.6 | Verification methodology                                                  | 81  |

|   |     | 4.6.1 Iterative refinement                                                | 83  |

|   |     | 4.6.2 Off-line timing analysis of failures                                | 85  |

|   |     | 4.6.3 Incorporation of relative timing constraints                        | 86  |

|   |     | 4.6.4 Back-annotation                                                     | 87  |

|   |     | 4.6.5 Correctness                                                         | 87  |

|   |     | 4.6.6 Convergence                                                         | 88  |

|   | 4.7 | Conclusions                                                               | 90  |

| 5 | EXF | PERIMENTAL RESULTS                                                        | 93  |

|   | 5.1 | A brief introduction to TRANSYT                                           | 94  |

|   |     | 5.1.1 Representation of LzTSs with boolean algebras                       | 95  |

|   |     | 5.1.2 TRANSYT input format                                                | 98  |

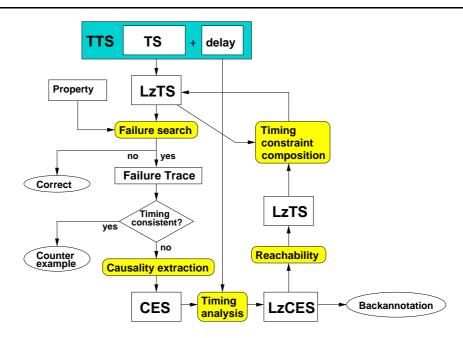

|   | 5.2 | An example with forward unfolding                                         | 102 |

|   |     | 5.2.1 Model of a timed PN                                                 | 104 |

|   |     | 5.2.2 Verification                                                        | 106 |

|   |     | 5.2.3 Discussion                                                          | 111 |

|   | 5.3 | Verification of complex-gate decompositions in speed-independent circuits | 112 |

|   |     | 5.3.1 Speed-independent circuits                                          | 112 |

|   |     | 5.3.2 Experimental set-up                                                 | 113 |

|   |     | 5.3.3 The sbuf-read-ctl controller                                        | 114 |

Contents

|   |     | 5.3.4                           | Model of an STG                                                     | 115 |

|---|-----|---------------------------------|---------------------------------------------------------------------|-----|

|   |     | 5.3.5                           | Model of the circuit                                                | 117 |

|   |     | 5.3.6                           | Specification of properties                                         | 118 |

|   |     | 5.3.7                           | Verification                                                        | 121 |

|   |     | 5.3.8                           | Results and discussion                                              | 125 |

|   | 5.4 | Verific                         | ation of relative timing assumptions                                | 127 |

|   |     | 5.4.1                           | Synthesis of asynchronous circuits with relative timing assumptions | 128 |

|   |     | 5.4.2                           | The VME bus controller                                              | 131 |

|   |     | 5.4.3                           | Models and properties                                               | 134 |

|   |     | 5.4.4                           | Verification                                                        | 137 |

|   |     |                                 | Discussion                                                          | 142 |

|   | 5.5 | Conclu                          | ısions                                                              | 144 |

| 6 | CON | APOSI'                          | TIONAL VERIFICATION                                                 | 147 |

|   | 6.1 | Introd                          | uction                                                              | 148 |

|   | 6.2 | The II                          | PCMOS architecture                                                  | 149 |

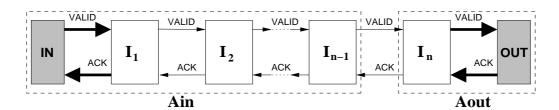

|   |     | 6.2.1                           | IPCMOS pipelines                                                    | 149 |

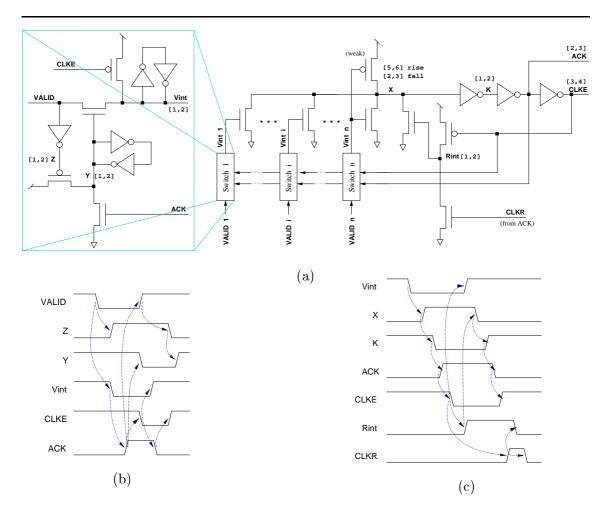

|   |     | 6.2.2                           | Strobe circuit                                                      | 152 |

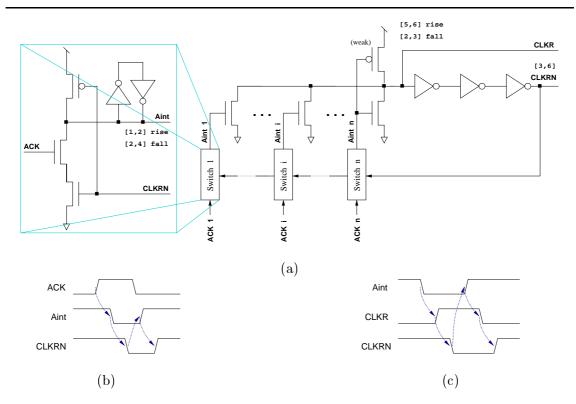

|   |     | 6.2.3                           | Reset circuit                                                       | 153 |

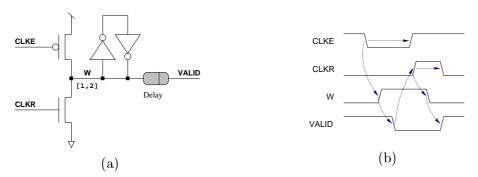

|   |     |                                 | Valid circuit                                                       | 155 |

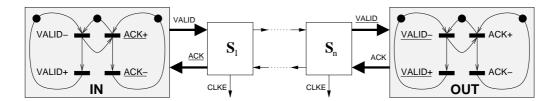

|   |     |                                 | The environment modules                                             | 155 |

|   |     | 6.2.6                           | About complexity                                                    | 156 |

|   | 6.3 | -                               | ositional verification                                              | 156 |

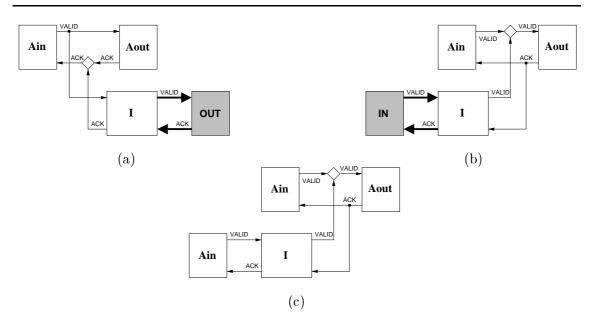

|   |     | 6.3.1                           | Framework                                                           | 158 |

|   | 6.4 | Verific                         | ation of IPCMOS pipelines                                           | 159 |

|   |     |                                 | Verification strategy                                               | 159 |

|   |     |                                 | Abstractions                                                        | 161 |

|   |     | 6.4.3                           | Assume-guarantee verification                                       | 162 |

|   | 6.5 |                                 | ation of a stage                                                    | 165 |

|   |     | 6.5.1                           | Modeling CMOS circuits                                              | 165 |

|   |     |                                 | Modeling IPCMOS circuits                                            | 169 |

|   |     | 6.5.3                           |                                                                     | 170 |

|   | 6.6 | Conclu                          | ısions                                                              | 173 |

| 7 | CON | ICLUS                           | IONS                                                                | 175 |

|   | 7.1 | $\operatorname{Introd}$         | uction                                                              | 176 |

|   | 7.2 | $\operatorname{Contri}$         | butions                                                             | 177 |

|   | 7.3 | $\operatorname{Futur} \epsilon$ | e research                                                          | 179 |

| A | TIM | ING A                           | NALYSIS                                                             | 183 |

|   | A.1 | Introd                          | uction                                                              | 184 |

|   | A.2 | Timin                           | g analysis on acyclic graphs                                        | 186 |

|   |     |                                 |                                                                     |     |

X CONTENTS

| В            | ON   | THE E                 | ENABLING-COMPATIBLE PRODUCT                           | 189 |  |

|--------------|------|-----------------------|-------------------------------------------------------|-----|--|

|              | B.1  | Enabl                 | ing-compatible product                                | 190 |  |

|              |      | B.1.1                 | T                                                     | 190 |  |

|              |      | B.1.2                 | Refining the reachability space by timing constraints | 191 |  |

|              | B.2  | Symbo                 | olic representation                                   | 192 |  |

|              |      | B.2.1                 | Encoding of a LzTS                                    | 193 |  |

|              |      | B.2.2                 | Encoding the state space of a LzCES                   | 193 |  |

|              | B.3  | $\operatorname{Comp}$ | outation of the new transition relations              | 194 |  |

|              |      | B.3.1                 | Transitions entering the timed domain                 | 194 |  |

|              |      | B.3.2                 | Staying inside the timed domain: no synchronization   | 195 |  |

|              |      | B.3.3                 | Staying inside the timed domain: synchronization      | 195 |  |

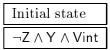

|              |      | B.3.4                 | Transitions re-entering the timed domain              | 196 |  |

|              |      | B.3.5                 | Exiting or staying outside the timed domain           | 196 |  |

|              |      | B.3.6                 | New transition relation                               | 196 |  |

|              |      | B.3.7                 | Lazy events                                           | 196 |  |

|              |      | B.3.8                 | Initial state                                         | 197 |  |

| $\mathbf{C}$ | VE   | RIFIC.                | ATION-RELATED COMMANDS                                | 199 |  |

|              | C.1  | Failur                | e analysis                                            | 200 |  |

|              |      | C.1.1                 | The add_fail command                                  | 200 |  |

|              |      | C.1.2                 | The check_fails command                               | 200 |  |

|              |      | C.1.3                 | The print_fails command                               | 201 |  |

|              | C.2  | Analy                 | sis of delay relations                                | 201 |  |

|              | C.3  | The <b>u</b>          | verif command                                         | 202 |  |

|              | C.4  | The t                 | verif command                                         | 203 |  |

|              |      | C.4.1                 | Output                                                | 204 |  |

|              |      | C.4.2                 | Construction of the failure trace                     | 209 |  |

|              |      | C.4.3                 | Construction of the LzCES                             | 209 |  |

|              |      | C.4.4                 | Timing analysis                                       | 211 |  |

|              |      | C.4.5                 | Miscellaneous                                         | 211 |  |

|              |      | C.4.6                 | Summary of the tverif command                         | 212 |  |

| REFERENCES   |      |                       |                                                       |     |  |

| G            | LOSS | SARY (                | OF SYMBOLS                                            | 227 |  |

# LIST OF FIGURES

| 1 | INTF | RODUCTION                                                        | 1  |

|---|------|------------------------------------------------------------------|----|

|   | 1.1  | Automaton modeling a modulo 3 counter.                           | 4  |

|   | 1.2  | Iterative design flow.                                           | 6  |

|   | 1.3  | The theorem proving approach.                                    | 9  |

|   | 1.4  | The model checking approach.                                     | 10 |

| 2 | MOL  | ELS FOR CONCURRENT SYSTEMS                                       | 17 |

|   | 2.1  | An example of transition system.                                 | 19 |

|   | 2.2  | An example of timed transition system.                           | 21 |

|   | 2.3  | Portion of the timed state space of a TTS.                       | 23 |

|   | 2.4  | An example of lazy transition system.                            | 25 |

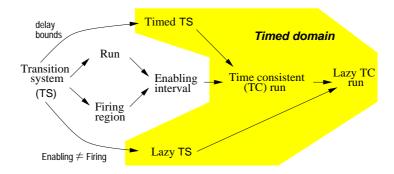

|   | 2.5  | Relations among the main notions related to transition systems.  | 27 |

|   | 2.6  | An example of Petri net.                                         | 28 |

|   | 2.7  | Reachability graph of a Petri net                                | 31 |

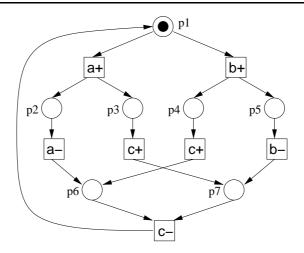

|   | 2.8  | Petri net of Figure 2.6 with labeled transitions.                | 32 |

| 3 | VER  | IFICATION OF TIMED SYSTEMS                                       | 35 |

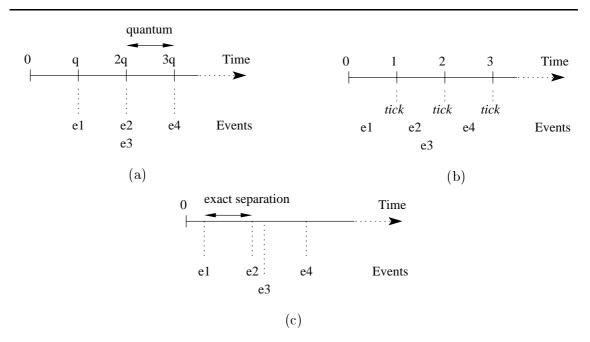

|   | 3.1  | Three representations of time.                                   | 38 |

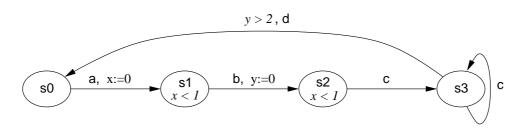

|   | 3.2  | An example of timed automaton.                                   | 40 |

|   | 3.3  | A simple automaton with atomic propositions.                     | 43 |

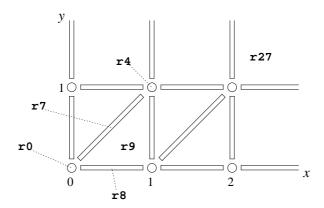

|   | 3.4  | Regions for two clocks.                                          | 47 |

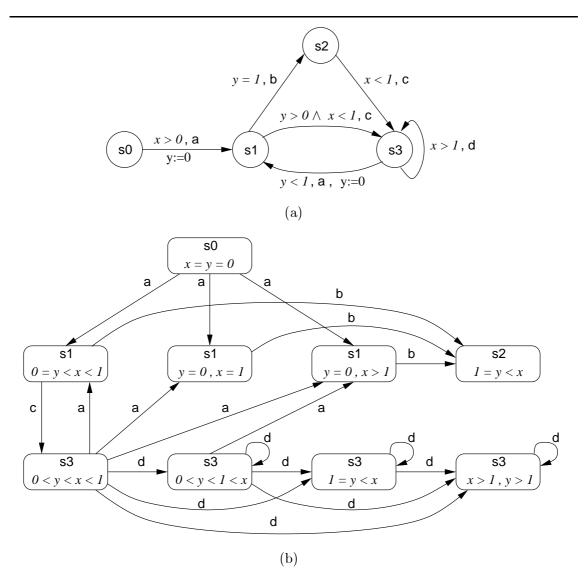

|   | 3.5  | Region automaton.                                                | 49 |

|   | 3.6  | Zone automaton.                                                  | 50 |

| 4 | VER  | IFICATION WITH RELATIVE TIMING                                   | 53 |

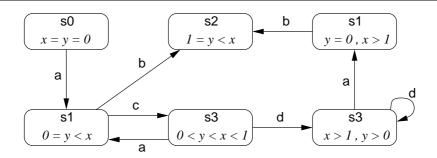

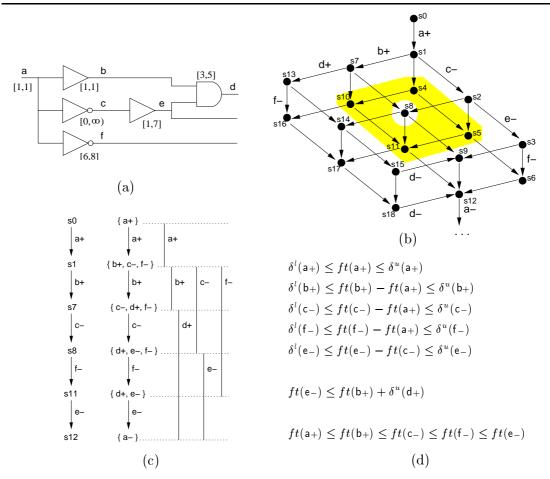

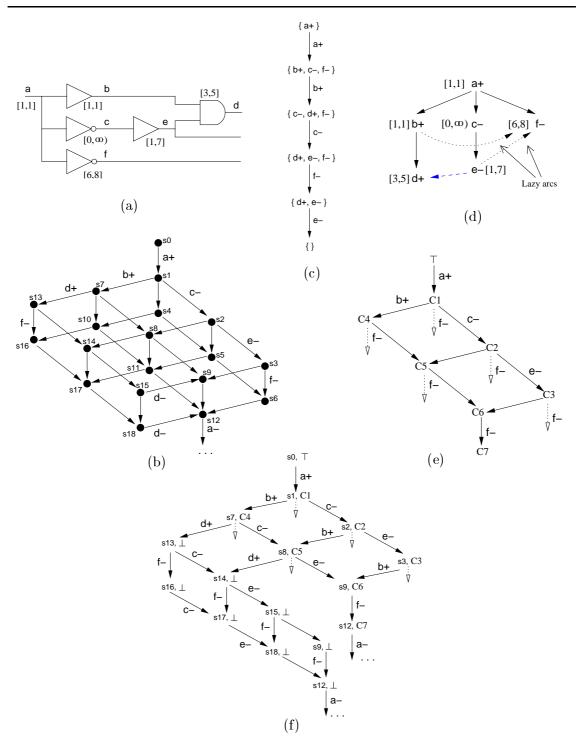

|   | 4.1  | Relative timing in the synthesis of circuits.                    | 56 |

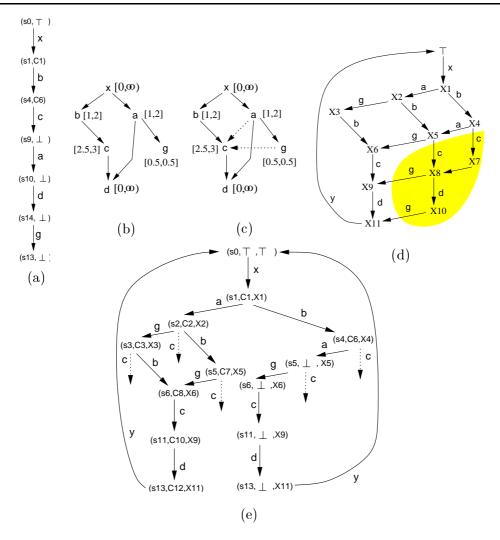

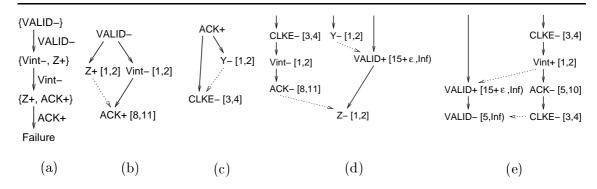

|   | 4.2  | Example of verification with relative timing.                    | 59 |

|   | 4.3  | Example of verification with relative timing (first iteration).  | 60 |

|   | 4.4  | Example of verification with relative timing (second iteration). | 61 |

|   | 4.5  | From traces to language refinement.                              | 63 |

|   | 4.6  | Relation between runs and traces.                                | 64 |

|   | 4.7  | Enabling and disabling in a trace                                | 65 |

xii List of figures

|   | 4.8  | Circuit with a potential disabling.                                | 67  |

|---|------|--------------------------------------------------------------------|-----|

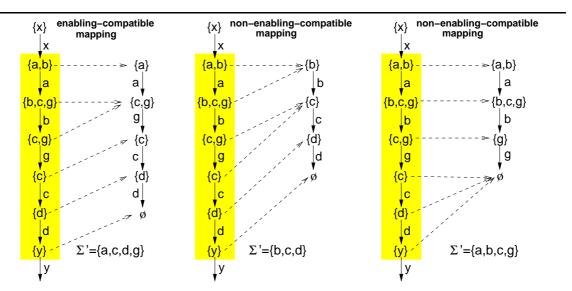

|   | 4.9  | Enabling-compatible and non-enabling-compatible mapping.           | 68  |

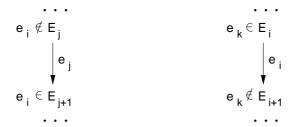

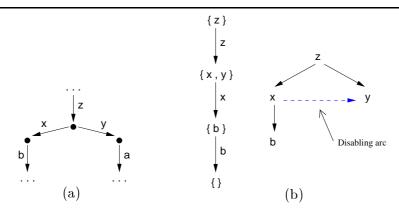

|   | 4.10 | Symmetric vs. asymmetric disabling.                                | 71  |

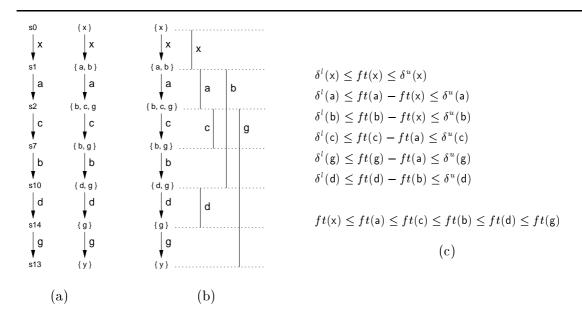

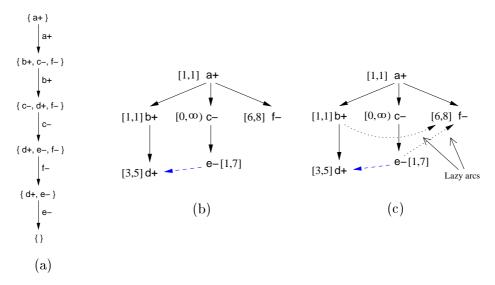

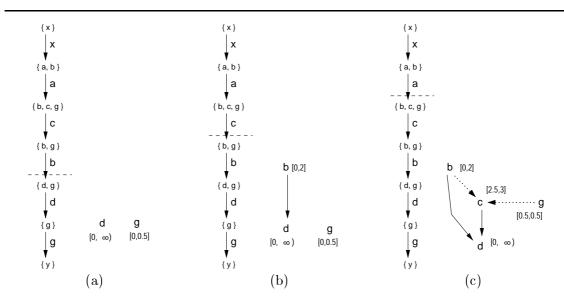

|   | 4.11 | Timing analysis over a CES and resulting lazy CES.                 | 74  |

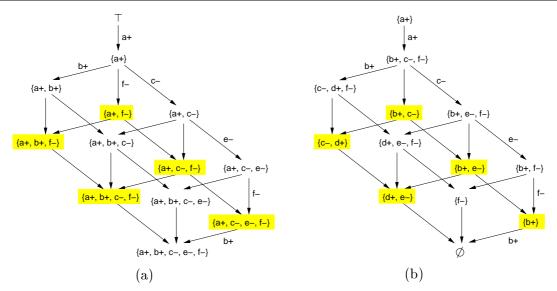

|   | 4.12 | Graphs of reachable configurations and enablings.                  | 78  |

|   | 4.13 | Step by step refinement by enabling-compatible product.            | 82  |

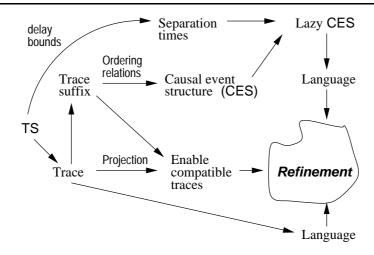

|   | 4.14 | Flow of the verification methodology.                              | 83  |

|   | 4.15 | Main algorithm of the relative timing-based verification approach. | 84  |

|   | 4.16 | Algorithm for the derivation of a LzCES from a trace.              | 84  |

|   | 4.17 | Generation of the sufficient shortest suffix of a trace.           | 85  |

|   | 4.18 | Example of a nodal and a not nodal point.                          | 89  |

| 5 | EXPE | RIMENTAL RESULTS                                                   | 93  |

|   | 5.1  | A binary-encoded LzTS.                                             | 98  |

|   | 5.2  | TRANSYT input file for the LzTS of Figure 5.1.                     | 100 |

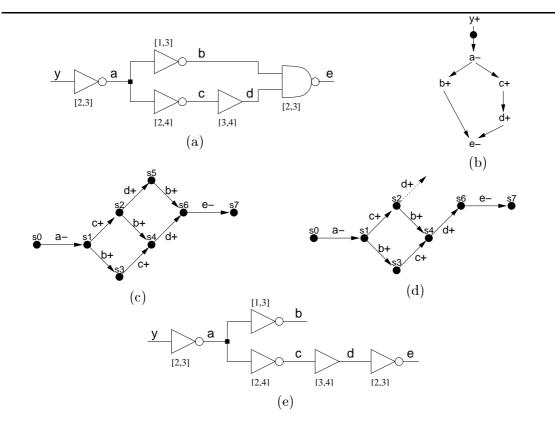

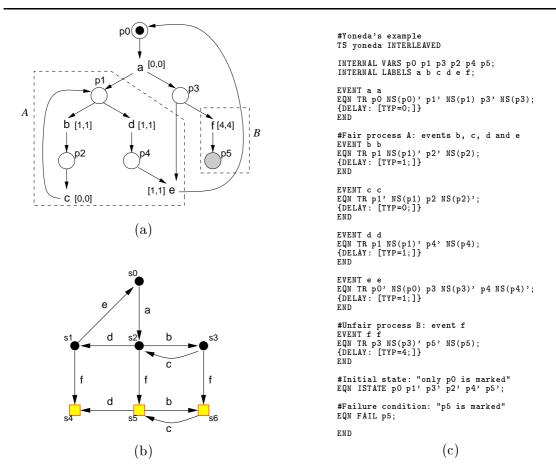

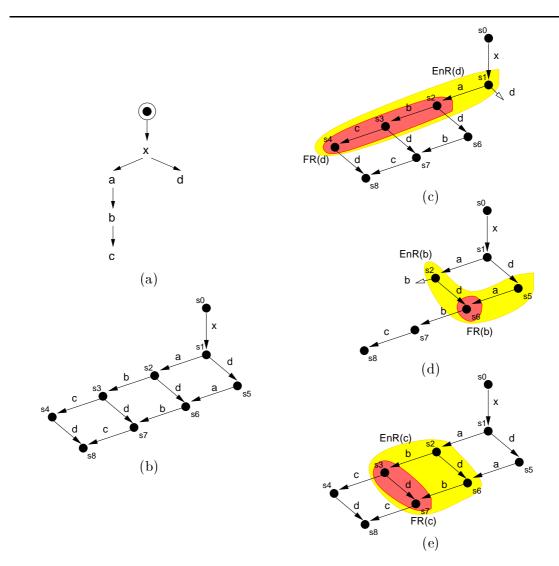

|   | 5.3  | Yoneda's example.                                                  | 103 |

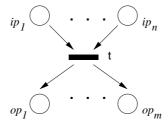

|   | 5.4  | Transition of an PN with its input and output places.              | 104 |

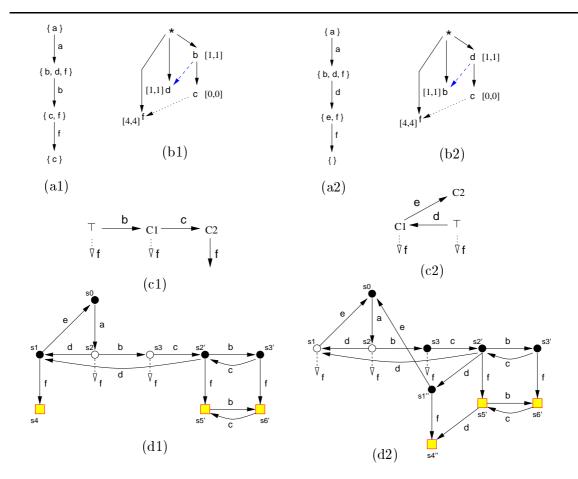

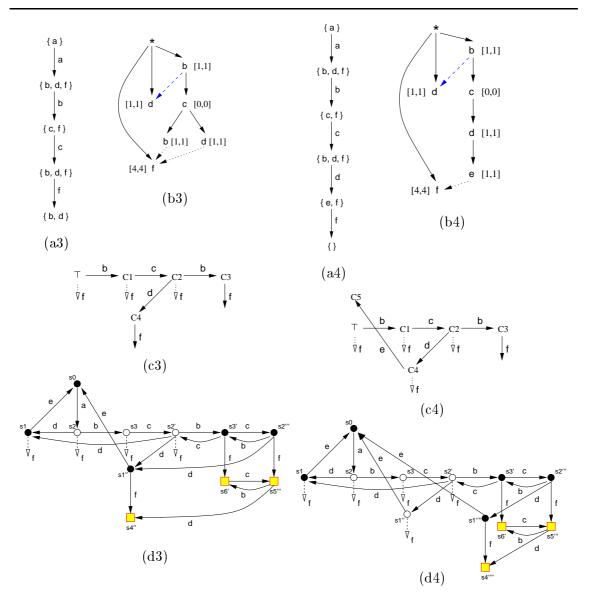

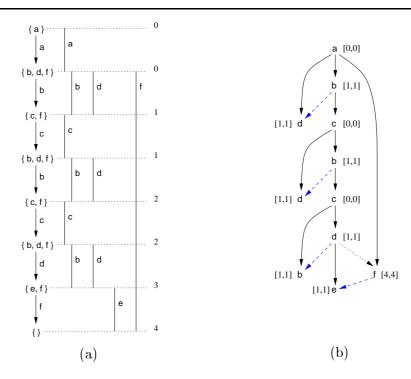

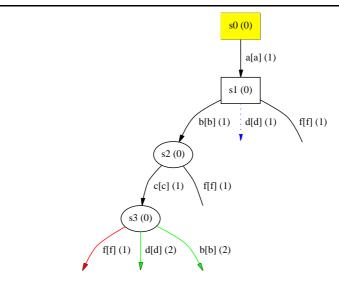

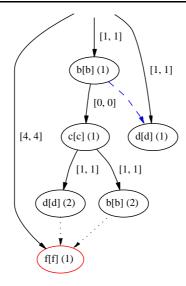

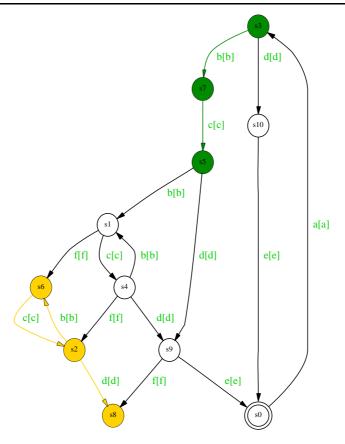

|   | 5.5  | Yoneda's example: first and second refinements.                    | 107 |

|   | 5.6  | Yoneda's example: third and forth refinements.                     | 108 |

|   | 5.7  | Yoneda's example: counterexample trace proving incorrectness.      | 110 |

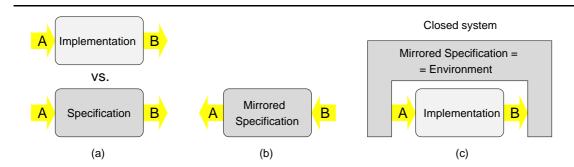

|   | 5.8  | System vs. specification verification scheme.                      | 113 |

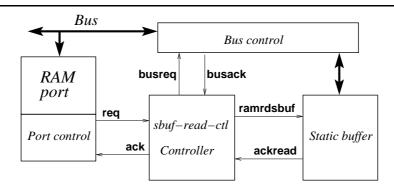

|   | 5.9  | Input-output interface of the sbuf-read-ctl controller.            | 114 |

|   | 5.10 | STG specification of the sbuf-read-ctl controller.                 | 116 |

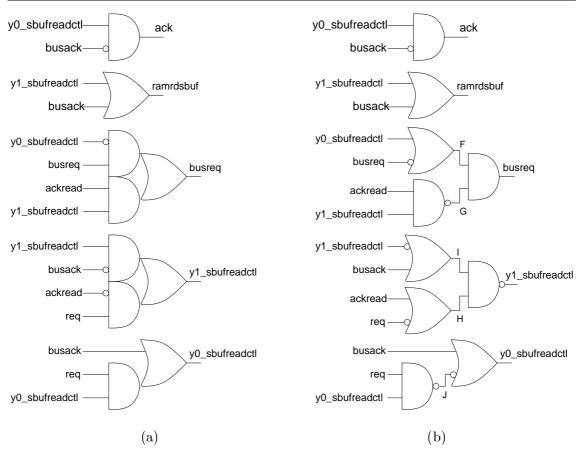

|   | 5.11 | Two implementations of the sbuf-read-ctl controller.               | 118 |

|   | 5.12 | TRANSYT input file for the circuit of Figure 5.11 (b).             | 119 |

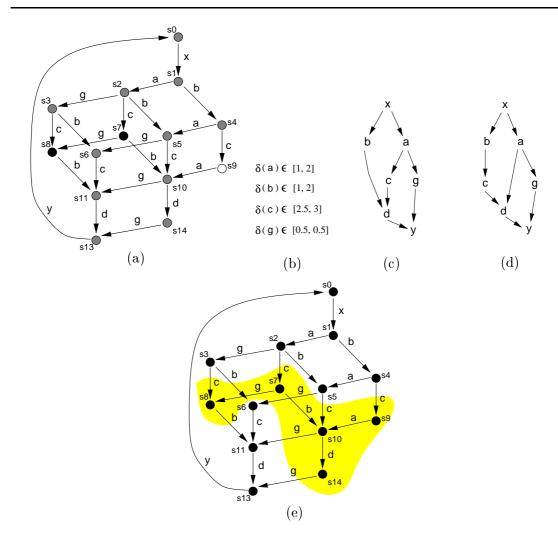

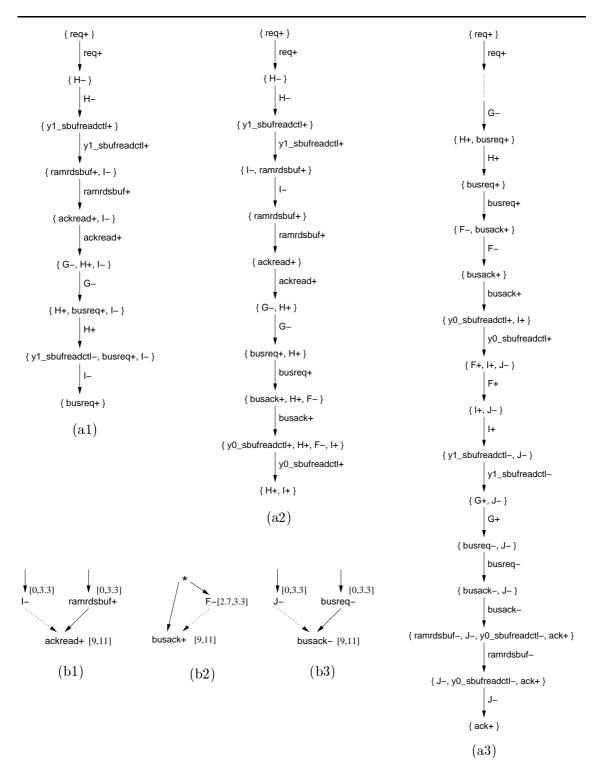

|   | 5.13 | Three refinements for the sbuf-read-ctl controller.                | 124 |

|   | 5.14 | An example of relative timing assumptions.                         | 129 |

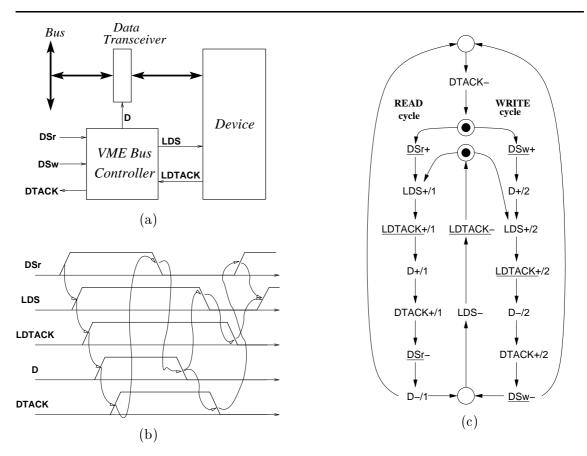

|   | 5.15 | VME bus controller.                                                | 132 |

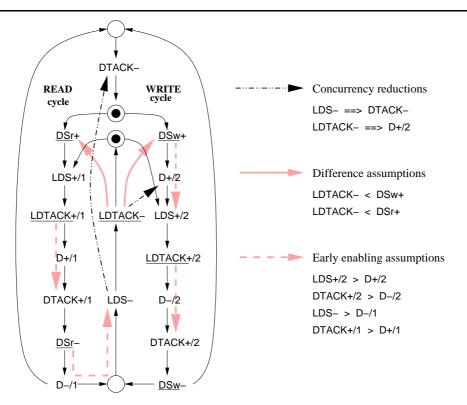

|   | 5.16 | Timing assumptions for the synthesis of the VME bus controller.    | 133 |

|   | 5.17 | Implementation of the VME bus controller with timing assumptions.  | 134 |

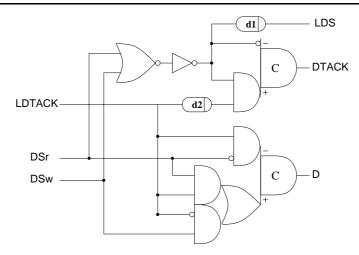

|   | 5.18 | TRANSYT input files for the VME bus controller.                    | 135 |

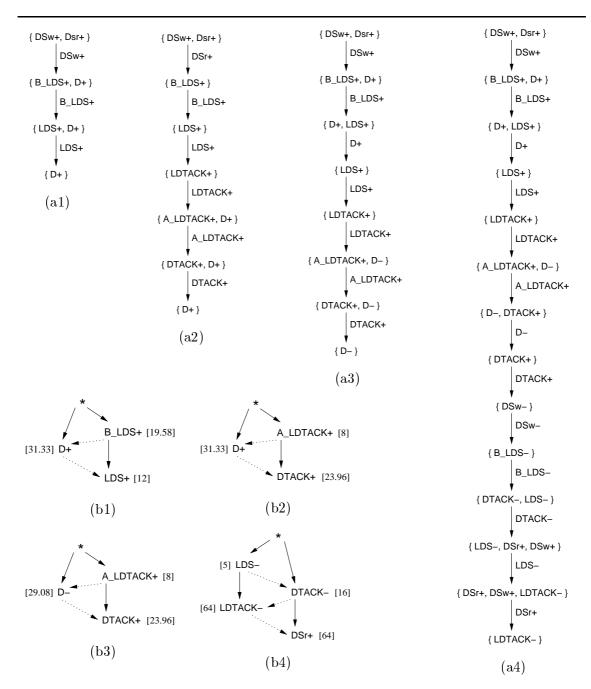

|   | 5.19 | First four refinements for the VME bus controller.                 | 141 |

|   | 5.20 | Last four refinements for the VME bus controller.                  | 143 |

| 6 | COMF | POSITIONAL VERIFICATION                                            | 147 |

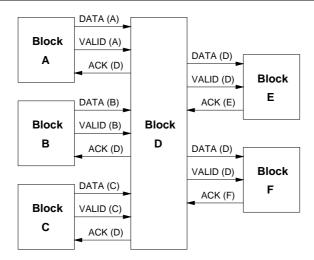

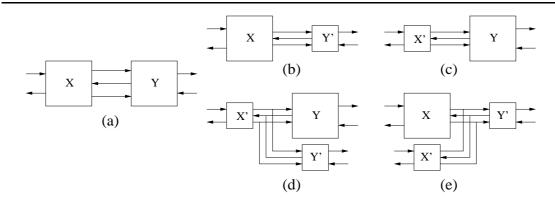

|   | 6.1  | General block-level interlocking scheme.                           | 149 |

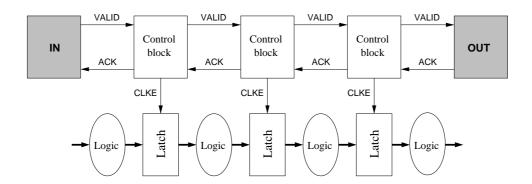

|   | 6.2  | Linear IPCMOS architecture.                                        | 150 |

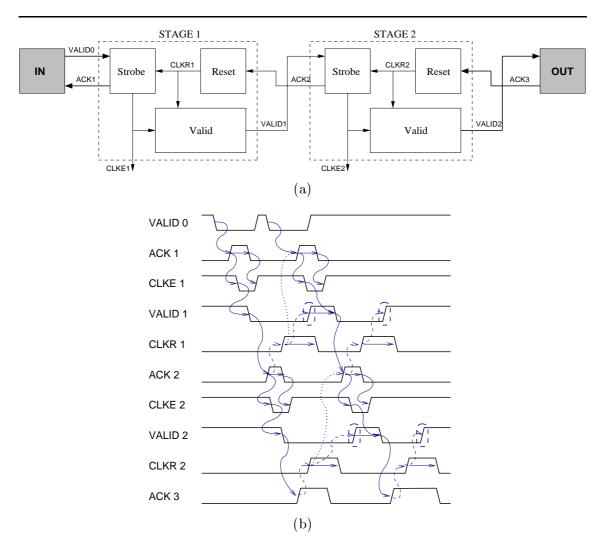

|   | 6.3  | Detailed 2-stage IPCMOS pipeline and waveform of its behavior.     | 151 |

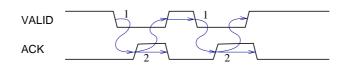

|   | 6.4  | Two-phase handshake mechanism.                                     | 152 |

|   | 6.5  | The strobe circuit in detail.                                      | 153 |

|   | 6.6  | The reset circuit in detail.                                       | 154 |

| List of figures | X | iii |

|-----------------|---|-----|

|                 |   |     |

|              | 6.7  | The valid circuit in detail.                                                              | 155 |

|--------------|------|-------------------------------------------------------------------------------------------|-----|

|              | 6.8  | $STGs$ modeling the pulse-based behavior of the $\mathit{IN}$ and $\mathit{OUT}$ modules. | 155 |

|              | 6.9  | Assume-guarantee verification using abstractions.                                         | 157 |

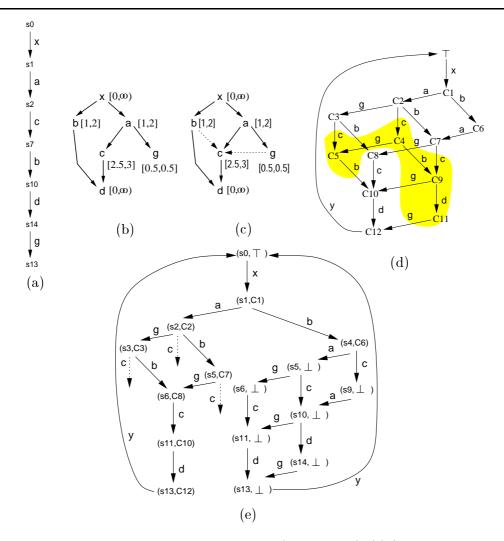

|              | 6.10 | Pipeline verification using abstractions.                                                 | 160 |

|              | 6.11 | STGs modeling the abstractions $A_{in}$ and $A_{out}$ .                                   | 161 |

|              | 6.12 | Scheme of the guarantee part of the verification.                                         | 163 |

|              | 6.13 | LzCES used to prove correctness of the strobe switch circuit.                             | 170 |

| A            | TIMI | NG ANALYSIS                                                                               | 183 |

|              | A.1  | Classes of timing analysis problems.                                                      | 184 |

|              | A.2  | Timing analysis on an acyclic graph.                                                      | 187 |

| $\mathbf{C}$ | VERI | FICATION-RELATED COMMANDS                                                                 | 199 |

|              | C.1  | An example of DOT file for a failure trace.                                               | 205 |

|              | C.2  | An example of DOT file for a LzCES.                                                       | 207 |

|              | C.3  | An example of DOT file for the lazy state space of a system.                              | 208 |

|              |      |                                                                                           |     |

# LIST OF TABLES

| 5 | EXPERIMENTAL RESULTS       |                                                                      |     |

|---|----------------------------|----------------------------------------------------------------------|-----|

|   | 5.1                        | Failure situations in sbuf-read-ctl along the verification.          | 122 |

|   | 5.2                        | Experimental results for the verification of asynchronous circuits.  | 125 |

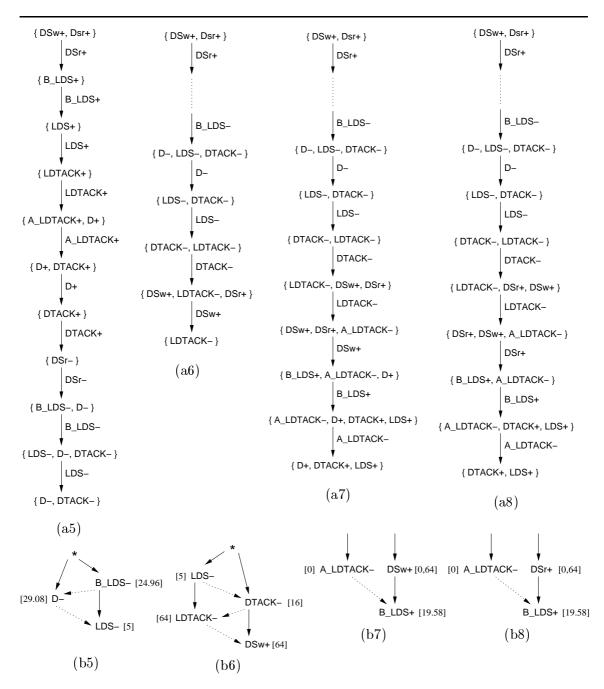

|   | 5.3                        | Failure situations in the VME bus controller along the verification. | 139 |

| 6 | COMPOSITIONAL VERIFICATION |                                                                      | 147 |

|   | 6.1                        | Summary of the results for the 5 steps of the verification.          | 164 |

|   | 6.2                        | Model of the <i>strobe</i> circuit.                                  | 166 |

|   | 6.3                        | Model of the strobe switch circuit.                                  | 166 |

|   | 6.4                        | Model of the reset circuit.                                          | 167 |

|   | 6.5                        | Model of the reset switch circuit.                                   | 167 |

|   | 6.6                        | Model of the valid circuit                                           | 167 |

# **ABSTRACT**

The thesis presents a new theory and methodology for the formal verification of safety properties in timed systems. The correct operation of such systems not only depends on a set of functional properties but also on certain assumptions about the delays of the components of the system and the response times of the environment in which the system operates. The verification of this type of systems typically involves several computationally hard problems. In particular, the combinatorial state explosion problem becomes exacerbated by the time dimension.

The theory that supports the proposed verification approach extends the conventional BDD-based symbolic methods to the verification of timed systems, modeled by means of timed transition systems. The theory is based on the relative timing paradigm, which instead of considering exact time differences in the occurrence of events, considers the effect of delays in terms of relative orderings between events. For example, in order to guarantee that a race is not propagated in a digital circuit, it is often sufficient to check that certain signal switches before another, instead of identifying the exact instants of time in which both signals switch. Moreover, the timing information does not need to computed for the overall system, but only locally for the part of the system involved in the proof or disproof of a given property. This is possible thanks to a crucial observation, that the set of executions of a transition system can be covered by a set of partial orders. As a consequence, only a subset of the events of the system is involved in the proof of a property and the timing analysis can be carried out very efficiently.

Conventional methods for the verification of timed systems rely on the computation of the exact timed state space of the system as the first step of the analysis. Although efficient techniques have been devised to overcome the complexity issue (e.g. difference bound matrices), symbolic methods cannot be easily applied. Thus, the combinatorial time-state explosion problem often limits the applicability of such methods to moderate-size systems.

Instead, the approach proposed in the thesis relies on an incremental refinement of the untimed state space of the system, so that timing information is incorporated as soon as it is needed. The timing information is derived by an efficient off-line timing analysis over small sets of events. The refined state space is captured under the model of lazy transition

xviii Abstract

system, which allows an efficient representation of the timed domain using conventional symbolic methods. As a consequence, the approach can be potentially applied to bigger systems or to systems with more level of detail, than those that can be handled by similar methods for the verification of timed systems. Moreover, the incremental nature of the approach provides a good way to obtain at least partial results even on systems for which complete solutions could be too complex to compute.

A key feature of the proposed verification approach is that not only proves or disproves the correctness of a timed system. If the system is correct the set of relative timing relations used for the proof are provided. Such relations constitute a set of sufficient timing constraints that guarantee the correctness of the system. On the other hand, if the system is incorrect, a counterexample failure trace is provided. The most important aspect of all this feedback is that it can be used as valuable back-annotation information along the design process. This feature, which allows to bridge the gap between verification and design, constitutes another differential aspect of our verification approach when compared to other equivalent verification methods.

The verification approach has been fully implemented in an experimental CAV tool called TRANSYT. The tool can handle hierarchical and distributed modular systems which can inter-operate by a variety of communication mechanisms. TRANSYT has successfully proved its functionality as well as the validity of the overall verification approach, by verifying a number of timed asynchronous circuits with up to more than 10<sup>6</sup> untimed states. The experiments cover, for example, the verification of: complex-gate decompositions in quasi-speed-independent asynchronous circuits, delay-reset domino circuits, pulse-based systems, circuits optimized for speed using timing assumptions, etc. Additionally, compositional verification methods have been combined with the basic verification approach in order to tackle the size/complexity issues involved in the verification of complex timed systems. Thus, abstractions, assume-guarantee reasoning and mathematical induction have been used to prove the correctness the IPCMOS architecture. It is a scalable pipelined architecture which is aimed to the interconnection of different clock zones in a system.

Thanks to the rather theoretical nature of the proposed verification approach, its potential applicability covers a wider range of systems than those cited above, such as: custom transistor-level circuits that exploit the technology limits for performance, complex digital structures where synchronization is a crucial issue (e.g. dynamic MOS), asynchronous and GALS-type systems, real-time systems, etc.

# ACKNOWLEDGMENTS

If I have seen further than others, it is because I was standing upon the shoulders of giants.

—Isaac Newton - Letter to a friend, 1676

The first person that deserves my acknowledgment is my supervisor Jordi Cortadella. He introduced me to the world of asynchronous circuits, Petri nets, formal verification, etc. back in 1993 when I was still an undergraduate student. His deep insight into the subject of this thesis provided me a lot of helpful suggestions. Without his guidance and kind encouragement this thesis would have never been possible.

I am specially indebted to my other supervisor, Enric Pastor. His continuous support and friendship have helped me to overcome the (technical and personal) difficulties during the critical phases of this work.

My gratitude also to Alex Kondratyev and Alexander Smirnov for their contributions to the theoretical soundness and the practical implementation of this work, respectively. And to Luciano Lavagno, Alex Yakovlev and Alexander Taubin, for their kindness hosting me in respective visits to the *Politecnico di Torino*, the University of Newcastle and the University of Aizu. The numerous insightful discussions with them about different research topics have contributed this thesis in a number of ways.

Thanks to the other members of the CAD/VLSI group at the Department of Computer Architecture of the Technical University of Catalonia —Rosa Badia, Fermín Sánchez and Josep Carmona— and former members —Oriol Roig and Enric Musoll. Along these years they have provided me with the kind of environment that makes work a much more pleasant experience.

Thanks also to the reviewers at Department of Computer Architecture —Rosa Badia, Antonio González and Antonio Juan Hormigo— and the external reviewers —Abelardo Pardo and Supratik Chakraborty. They read carefully the preliminary versions of this thesis giving me valuable suggestions on the contents and the presentation of this work. And the members of the thesis committee for the effort they put into judging this thesis.

XX Acknowledgments

On the institutional and industry side I would like to acknowledge: the Ministry of Science and Technology of Spain under contracts CICYT-TIC 95-0419, CICYT-TIC 98-0410-CO-01 and CICYT-TIC 2001-2476-CO-03; the ACiD Working Group under contracts ESPRIT-7225, ESPRIT-21949 and IST-1999-29119; and Intel Corporation. They all are gratefully acknowledged for funding this research.

On the personal side my family deserves infinite gratitude: my father Antonio, my mother Adoración and my brother Jose. Thanks a lot for your efforts on infusing me the values of a good education and supporting all my studies along the years.

And the most effusive thanks to Nuria. During all this time she has been my best friend, providing lots of emotional support and love, and patiently suffering the numerous moments of solitude she has been forced to because of my work. This thesis is dedicated to her and our beloved son Pau.

Finally I would like to express my thanks to everyone I have not cited above but has helped me, directly or not, in the long way until this thesis has been completed. Thanks a lot to you all.

# INTRODUCTION

The real value of formal methods lies not in their ability to eliminate doubt, but in their capacity to focus and circumscribe it.

—John Rushby - [Rus93]

# Summary

This chapter introduces the generalities of the use of formal methods in the design and analysis of complex systems. Special attention is paid to the formal verification problem and its differentiation from simulation-based methods to prove the correctness of a design. The main approaches in the area of formal verification are also reviewed.

The chapter concludes with an overview of the motivations behind the work presented in the thesis, together with the main contributions.

#### 1.1 Introduction

Continuous advances in electronics and software engineering have driven the increase in size and functionality of systems into unprecedented levels of complexity. As a consequence the probability of introducing design error has increased considerably. This fact, combined with the ubiquity of such systems in our current lives makes necessary the development of techniques that help to reduce the probability of failures.

Formal methods appear as a promising tool in such context. They bring the formalization and reasoning power of mathematics and logic into system design. Thus, they can help in systematizing the early specifications, providing appropriate abstract models of systems, and allowing the development of automatic techniques for the analysis of such models. Currently, tools for the automatic synthesis of circuits, or the formal verification of real-time systems, to cite some, exist both in academia and in industry. Moreover, they are gaining acceptance in this latter context.

This thesis relies on the use of formal methods to contribute to the formal verification of systems whose correct behavior depends on timing issues. Formal verification, although it is not a mainstream research topic, is getting increasing attention from industry due to several reasons.

In contrast to simulation, formal verification consists in building a mathematically-based proof that a system (implementation) behaves according to a given specification. For the check, all possible behaviors of the system must be taken into consideration, leading to the well-known state-explosion problem. In systems with a finite number of states, this problem is often alleviated by using symbolic techniques to implicitly enumerate all reachable states. Abstraction methods are also a common technique used to reduce the complexity of the model, by hiding those implementation details that are irrelevant to the properties begin verified.

The correctness of timed systems depends on the actual response times of the system and not only on its functional behavior. Therefore, time becomes an essential dimension in the verification problem and the complexity issue is exacerbated. For example, the problem of computing the language of a timed system modeled as a timed automata has been proved to be PSPACE-complete.

This thesis proposes a novel formal verification approach that extends the applicability of the conventional methods based on symbolic reachability analysis to timed systems. A major issue is the use of relative timing, which instead of considering exact delay separations, considers the effect of delays in a system in terms of relative ordering of events (e.g. a happens before b). This leads to the model of lazy transition systems which allows to represent the time domain in an efficient way, without increasing complexity when dealing with untimed systems.

1.2 Formal methods 3

#### 1.2 Formal methods

In recent years, hardware and software systems have experimented a continuous growth in size and functionality. Due to this increase of complexity the probability to introduce design errors has also increased considerably. Often, such systems are used in applications where a failure has unacceptable consequences. Errors in electronic commerce systems, communication networks, traffic control systems, medical instruments, etc. may be the cause of important loss of money, time, or even human lives. One well-known example is the error found in the divider unit of the *Pentium* microprocessor in the fall of 1994, which correction and replacement costed *Intel Corp.* about 475 million US dollars [Pet97]. Another famous case is the launch failure of the *Ariane 5* rocket, which exploded 37 seconds after lit-off on June 1996 due to a software error that interpreted the flight altitude as a 16-bit integer when it was meant to be a 64-bit real [Lio96]. A long list of similar incidents related to failures in computers and electronic systems can be found in [Neu].

A major goal of engineering is to provide mechanisms that allow the construction of reliable systems despite of their complexity. One way of achieving this goal is to use formal methods, which involve mathematically-based languages, techniques and tools for the modeling, specification, design and verification of systems. The use of formal methods for the specification of a system requires certain precision, due to which ambiguities can be avoided along the design process. Also, the strict syntax and semantics provided by the formalisms often forces the designers to achieve a deep understanding of the system, in such a way that the relevant features are properly captured. On the other hand, the formal nature of the analysis on the resulting implementation provides an objective point of view about the degree of correctness of the system with respect to the original specification. Altogether provides a systematic approach for the correct construction of systems, which is suitable for its automatization by means of CAD/CAV tools.

Formal methods per se do not guarantee the construction of systems of better quality. In order to benefit from formal methods, appropriate formalisms for the specific application domain must be chosen. Also, if CAD/CAV tools are used one must remember that they can be buggy and comparisons between more than one tool can be mandatory. Moreover, the results of the formal analysis to check the correctness of the results obtained along the design, must be properly interpreted, and this is not always an easy or evident task.

Finally, certain techniques such as formal verification often cannot be applied to a system as a whole, due to size/complexity considerations. Hence, a compromise is usually required between the size of the system and an adequate level of abstraction which allows the successful application of formal methods. When too complex systems are involved such that a complete formalization becomes intractable, the verification approach is used only for the most critical parts of the system. Moreover, high-level reasoning techniques

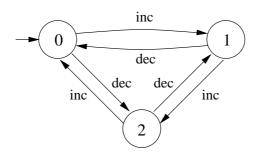

Figure 1.1 Automaton modeling a modulo 3 counter.

often come into play in order to allow dealing with the complexity issue at a higher level of abstraction.

## 1.2.1 Formal methods in the design process

Formal methods can be used along the complete design flow, from the early stages where the requirements are still being captured, until the latter stages where the system is yet implemented and full details are available.

Formal modeling consists in selecting a mathematical representation expressive enough to formalize a particular application, and powerful enough to explore and reason about the behavior of the system. This often requires the translation from a non-mathematical model, such as data-flow diagrams, pseudo-code, English text, etc., into formal models that include, among others: process algebras [BW90], Petri nets [Pet81], transition systems [Arn94], or timed automata [AD96]. The choice of one or another depends on the expressiveness power and the level of abstraction required for the application. Some of such modeling formalisms are discussed in more detail in Chapters 2 and 3.

**EXAMPLE 1.1** Informally, an automaton is a machine that evolves from one state to another under the action of transitions. For example, a module 3 counter can be modeled by an automaton with three states, one per counter value, and transitions that reflect the possible actions on the counter, i.e. increment or decrement its value (see Figure 1.1).

Notice that details such as if the counter is implemented by a software program or by a sequential circuit, for example, are abstracted away. Therefore, if the counter is finally implemented as a circuit, with a so abstract model, it will be impossible to reason about facts like if there is a short-circuit in a stack of transistors implementing a flip-flop, for example. However, the model may suffice if we want to check, for instance, if the counting process gets stuck after counting up to 2.

Formal specification covers the process of describing a system and its desired properties. The specification describes how the system is expected to work in the given environment. 1.2 Formal methods 5

The specification avoids unnecessary details and provides a general-enough description that can be adapted to system changes later on. This requires the use of a language with a mathematically defined syntax and semantics, which must be related to the chosen formal model. The kind of properties specified may include functional behavior, interface, timing behavior, performance, etc. Formal specifications may serve as a sound communication mechanism between the people involved along the life cycle of a system: customers, designers, implementer, testers, and so on. Examples of formal specification languages include Z [Spi88], CCS [Mil89], CSP [Hoa85], temporal logic [Pnu81, CE81], LOTOS [ISO89], etc. Some of them are more focused on the system description, whereas others are more suitable for the specification of properties. A good survey of the successful use of formal specifications in a variety of areas can be found in [CW96].

**EXAMPLE 1.1 (CONT.)** We may want to formulate a property that states that the modulo 3 counter of Figure 1.1 is free of deadlocks, i.e. it cannot end up stuck in any state. For example, such property is generally stated using the temporal logic CTL [CE81] by the formula AG EX true which can be read as: "whatever the state reached may be (AG), there will exist an immediate successor state (EX true)". See Section 3.4.1 for more details on CTL.

Formal analysis refers to techniques that can be used to calculate and explore the system behavior, and to verify properties of it. The main topic in this area of research is formal verification, in which two main approaches have traditionally coexisted. Namely, those approaches based in proof-theoretic automated deduction, such as theorem proving [GMW79]; and those based in finite state methods and state exploration, such as model checking [CGP00]. More details on both approaches are given in Section 1.3.2.

EXAMPLE 1.1 (CONT.) Using the appropriate mechanism, for example model-checking, it can be demonstrated that in the automata of Figure 1.1 which models a modulo 3 counter, every state satisfies the deadlock freeness property stated above.

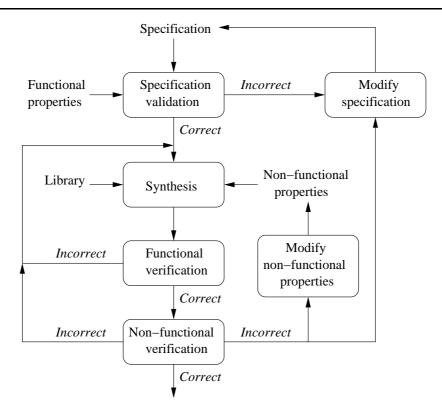

A typical design flow for concurrent systems consists of an iterative process in which both CAD/CAV tools and also the designer are involved. First, the process of verifying the specification is aimed at checking whether the system will not exhibit undesired behaviors. Then, the synthesis process generates an implementation of the system, using the primitives provided by some sort of *library*. The library may consist of different objects depending on the particular application: a set of logic gates to implement digital circuits, a set of assembler instructions of a given microprocessor, etc. Once the implementation is generated, the designer may want to prove if the *functionality* of the implementation is equivalent to that initially specified, under certain equivalence criteria. Despite of the

Figure 1.2 Iterative design flow.

equivalence with the specification, it is often required that the system satisfies other *non-functional* constraints. Requirement such as a particular response time, a limit in the amount of memory used by a program, etc. may be desirable at this point. In order to finally obtain a correct system that satisfies both functional and non-functional constraints, it may be required to modify the specification, resynthesizing the system, etc. Therefore, the whole process leads to an iterative design flow as that depicted in Figure 1.2.

The contributions of this thesis are focused on the verification of functional properties. The properties may depend on timing aspects of the system and/or of the environment in which it operates. The developed methods can be applied also to the verification of general functional properties and the validation of certain aspects of the specifications.

#### 1.3 Formal verification

Although more insightful details about the verification of timed systems are given in Chapter 3, this section provides some fundamentals about the formal verification problem in general.

1.3 Formal verification 7

## 1.3.1 Verification versus simulation

In order to check if a system implementation behaves according to its specification or satisfies certain properties, all possible behaviors of the system must be taken into consideration.

Nowadays, the most common approach for design verification is still computer-aided simulation. In simulation, input patterns are created which reflect typical or critical execution traces, the implementation is excited with such patterns, and the output is compared to that expected according to the specification. In case of sequential circuits, for example, all possible input combinations in every possible state must be analyzed. Since the number of required input patterns increases exponentially with the number of inputs and the number of states of the circuit, the approach is impractical even for circuits of moderate size. In consequence, the number of input patterns must be reduced and some design errors may remain undetected. Although simulation is the most intuitive approach for checking the correct behavior of a system, and is important for discovering failures quickly, it is not satisfactory when too complex designs need to be extensively analyzed.

An alternative to simulation is formal verification, which consists in building a mathematically-based proof that a system (implementation) behaves according to a given specification. Often, some simulation-based methods are also called "verification". To distinguish them from verification, the prefix "formal" is used to differentiate between both methods. The following example, taken from [Gor89], illustrates the fundamental difference between simulation and formal verification.

**EXAMPLE 1.2** The goal is to show that the expression  $(x+1)^2 = x^2 + 2x + 1$  holds, i.e. that both sides of the equation lead to the same result for all possible input values: A simulation based approach would check the equation using concrete values for x as:

| x  | $(x+1)^2$ | $x^2 + 2x + 1$ |

|----|-----------|----------------|

| 0  | 1         | 1              |

| 1  | 4         | 4              |

| 2  | 9         | 9              |

| 3  | 16        | 16             |

| 9  | 100       | 100            |

| 67 | 4624      | 4624           |

|    | • • •     |                |

However, as long as the equality must hold for all numbers – not even restricted to the subset of natural numbers as in the above table – simulation is not capable of establishing the validity of the equation.

In contrast, a formal mathematical proof can do exactly this by applying mathematical transformation rules as it is shown in the following table:

```

definition of square

(x+1)^2 = (x+1)(x+1)

2.

(x+1)(x+1) = (x+1)x + (x+1)1

definition of distributivity

(x+1)^2 = (x+1)x + (x+1)1

3.

substitution of 2. in 1.

(x+1)1 = x+1

4.

neutral element 1

(x+1)x = xx + 1x

5.

distributivity

(x+1)^2 = xx + 1x + x + 1

6.

substitution of 4. and 5. in 3.

7.

neutral element 1

(x+1)^2 = xx + x + x + 1

8.

substitution of 7. in 6.

xx = x^2

9.

definition of square

10.

x + x = 2x

definition of 2x

(x+1)^2 = x^2 + 2x + 1

substitution of 9. and 10. in 8.

11.

```

In simulation, a complete model of the system is used, however only a partial verification is achievable. In contrast, in formal verification a partial model of the appropriate abstraction level is used, and a complete proof can be obtained provided that model. As a consequence, it is often the case that both approaches are combined. Fast simulation may be used to discover simple or expected failures in the early stages of a design, whereas formal verification may be used to discover unusual or exotic failures in critical parts of the system.

Finally, recall that in general, in order to be able to perform a formal analysis and even be able to automate it, the specification, the implementation and the correctness relation must be in a form which allows a rigorous formal treatment.

## 1.3.2 Main approaches to formal verification

As cited above, there are two major approaches to formal verification, namely theorem proving and model checking. This section gives some general details on how these approaches work.

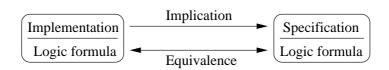

In theorem proving, both the system (implementation) and the properties (specification) are expressed as formulas in some mathematical logic. The logic is based in a set of axioms and provides a set of inference rules. Then, the approach consists in finding a proof of a given correctness relation between the implementation and the specification, following the axioms and the inference rules of the logic (see Figure 1.3). Therefore, it can deal directly with infinite state spaces, since no explicit state space exploration is required. However, the high complexity of the algorithms involved makes theorem proving applicable in practice only to moderate size or to particularly well-suited systems.

The proofs can be constructed automatically, although often require manual interaction of experts on the underlying logic and proof mechanisms. As a consequence, the process may become slow and often error-prone. In contrast, in the process of building the proof, the user achieves deep knowledge of the details of the system and the properties it must satisfy.

1.3 Formal verification 9

Figure 1.3 The theorem proving approach.

Theorem proving methods have not yet achieved widespread use outside universities. However, there are a number of representative theorem provers, such as Hol [GM93] or PVS [ORSS94], which have been used successfully in several domains.

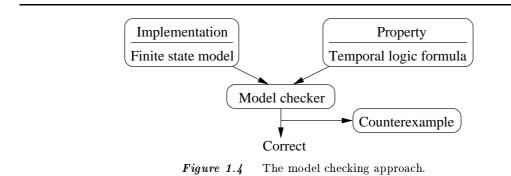

Model checking relies on building a finite model of a system and checking that the desired property holds in that model (see Figure 1.4). In temporal model checking [CE81, QS81] specifications are expressed in a temporal logic [Pnu81] and systems are modeled as finite state transition systems. An efficient search procedure is used to check if the transition system is a model for the specification. Other approaches use automata for both the specification and the system model. Then, the system is compared to the specification to determine if its behavior conforms to that of the specification. Different notions of conformance have been explored, such as language inclusion [Kur94], refinements [CPS93, Ros94], observational equivalence [CPS93], etc.

In contrast to theorem proving, model checking techniques are completely automatic. The check is performed by an exhaustive state space exploration which requires the use of specific algorithms and data structures to handle large state spaces. When the model checking algorithms fail to prove a given property, they are able to produce a counterexample, which indicates how is possible for the system to violate the specification. Counterexamples often correspond to subtle design errors and therefore can be used for debugging the system.

The main drawback of model checking is the so-called *state explosion* problem, which refers to the exponential blow up of the number of states of a system, such that it exceeds the available resources of a computer. Several approaches have been used so far to alleviate this problem. These include low-level techniques such as: symbolic representations of the state space [McM93] using binary decision diagrams (BDDs) [Bry86], partial order reductions [KP88, Pel96], etc. But also techniques that work at a higher level, such as: assume guarantee reasoning to exploit the modularity of the system [Pnu84], abstractions that remove irrelevant details for a particular analysis [Mel88], use of symmetries [CJEF96, ES96] and induction [BSV94, VK98] for systems with certain degree of regularity such as pipelines, etc. However, except for certain well-suited examples, only systems with about one hundred state variable can be handled as a whole. Clearly, this is far from the sizes of the current integrated circuits and microprocessors, for example. The verification problem

becomes much more difficult in the case of timed systems, because timing information must be taken into account when building the state space (see Chapter 3).

Several successful model checkers can be found nowadays, including: SMV [McM93] which was the first model checker to use BDDs allowing symbolic analysis; SPIN [Hol97] that takes advantage of partial orders for the verification of distributed algorithms; HSIS [ABC<sup>+</sup>94] which combines model checking with language inclusion; KRONOS [Yov97] and UPAAL [BLL<sup>+</sup>95] for the verification of real-time systems using timed automata; COSPAN [AK95] which verifies real-time systems by checking inclusion between  $\omega$ -automata; HYTECH [HHWT97] which allows to perform parametrized analysis, *i.e.* to determine the values of design parameters for which a linear hybrid automaton satisfies a temporal-logic requirement; and MOCHA [AHM<sup>+</sup>98] for modular verification of heterogeneous systems modeled by reactive modules.

The success of all these tools developed at universities, combined with the intensified need for formal methods has attracted the interest of the industry. As a result, internal tools have been developed (inside Motorola, Intel, IBM, etc.) and some commercial tools are also available (FORMALCHECK from Lucent Technologies, RULEBASE from IBM, INSIGHT from Crysalis Design, etc.).

Finally recall that there is no ideal verification approach which is powerful enough for all proof tasks and which, at the same time, allows completely automated proofs. Moreover, the choice of the best suited approach strongly depends on the actual verification problem.

# 1.4 Formal verification of timed systems

In systems whose correctness depends on a proper timing a quantitative notion of time must be incorporated both into the system models and also into the specification formalisms. Since time constitutes an additional source of complexity, the way it is represented has a crucial impact on the size of the resulting timed state space. Two main approaches exist for that purpose: discrete-time and continuous-time.

Formalisms based on the discrete-time notion map time onto the integer domain. They require to discretize time by choosing a fixed time quantum, so that the separation of two events in the timed domain is always a multiple of such quantum. In continuous-time models a non-negative real value is associated to each event of the system and to each reachable state, so that the exact bounds on the actual delays between the events can be expressed. The main advantage of discrete-time is that the timing analysis and timed state space exploration techniques are generally simpler than their counterparts for continuous-time. The main drawback is that determining the time quantum a priori may not be easy and therefore may compromise the accuracy of the model.

It has been mentioned above that the verification of concurrent systems typically suffers from the well known state-explosion problem. In systems with a finite number of states, this problem is often alleviated by using symbolic techniques to implicitly enumerate all reachable states [Bur92]. Abstraction methods are also a common technique used to reduce the complexity of the model, by hiding those implementation details that are irrelevant to the properties begin verified [Mel88]. However, when time becomes an essential dimension in the verification problem, complexity is drastically increased. The correctness of timed systems depends on the actual values of event delays and not only on its functional behavior. Typically, timing behavior is specified by a set of delays that determine the time duration between the initiation and the completion of an event. This is the valid model for the gates in a circuit, for example, in which gate delays denote the time between the enabledness of the gate and the actual change at the output.

Most approaches for the verification of timed systems rely on the construction of the timed reachability space. The problem is PSPACE-hard [AD94] since the number of timed states is infinite. Therefore, typical model checking algorithms are no longer applicable. Also, in order to overcome the complexity, finite representations of the timed state space must be provided. Although many techniques have been devised to alleviate the state-explosion problem and the additional complexity due to the time dimension, spectacular improvements in the resulting representations and algorithms are unlikely. In consequence, other high-level techniques (e.g. abstraction, compositional reasoning, induction, etc.) appear as the more promising ones for future developments in this area of research. Nevertheless, several methodologies and tools exist for the verification of timed systems.

## 1.5 Overview of the contributions

This thesis proposes a novel verification approach that extends the applicability of the conventional methods based on symbolic reachability analysis to timed systems. The approach is based on two fundamental facts:

■ The observation that the set of traces of a transition system can be covered by a set of marked graphs. This reduces the verification problem to that of: the timing analysis over small sets of events from which timing constraints that prove the correctness or incorrectness of a system can be derived; and the incorporation of such constraints into the system along an incremental refinement process.

■ The use of relative timing [SGR99] to represent the time domain in an efficient way. When considering precise delay bounds in timed systems, the complexity blow-up often causes synthesis and verification to become intractable problems, even for small systems. Instead, relative timing considers the effect of delays in a system in terms of relative ordering of events (e.g. a happens before b).

The verification approach can be briefly summarized as follows. Rather than calculating the exact timed state space, the verification approach performs an *off-line* timing analysis on a set of event structures [NPW81] that covers the traces leading to system failures. This timing analysis is efficiently performed by using McMillan and Dill's algorithm [MD92]. The resulting timing constraints are incorporated to the system in the form of relative timing information along a series of iterative refinements of the original untimed state space. Finally, if some of the traces leading to failure situations cannot be proved to be timing-inconsistent, then the system is incorrect and the failure trace is a counterexample.

Due to the incremental incorporation of timing information along the verification, our approach works with over-approximations of the actual timed state space of the system. Being the completely untimed state space used as starting point the roughest approximation possible. This fact allows the efficient verification of safety properties but makes impossible the verification of liveness properties, for example. For safety properties, it is enough to prove that no "undesired" situations (states) are reachable by the system. If "undesired" states do not appear in the over-approximations, they will neither appear in the exact timed state space, but not vice versa. Therefore, the verification can produce "false-negatives" but never "false-positives", i.e. it is conservative for safety properties. On the contrary, for liveness properties it must be proved that some "desired" situation is actually reachable. For that kind of proof, the exact timed state space (or an underapproximation for conservativeness) must be computed.

The idea of using event structures for timing analysis was already proposed in [KBS02]. However, no algorithm was presented that can handle a general class of transition systems for verification.

The approach presented here, not only verifies the correctness of the system with respect to a set of given properties, but also provides as back-annotation a set of timing constraints sufficient to prove correctness. This information is crucial in frameworks in which synthesis and verification are iteratively invoked to design systems that must meet functional and non-functional constraints.

We want to remark that the use of the method for the verification of untimed systems does not involve any additional overhead with respect to the conventional symbolic methods (e.g. [BCM<sup>+</sup>92]).

The resulting verification algorithms have been fully implemented in the CAV tool TRANSYT. The applicability of the approach and the functionality of the tool have been proved by verifying a number of timed asynchronous circuits [PCKP00].

The work on verification is completed by tackling the verification of a complex timed system, namely the IPCMOS architecture [SRC+00]. The IPCMOS circuit is a controller for asynchronous scalable architectures (such as pipelines, meshes, etc.) that can operate at frequencies of up to 4GHz thanks to a pulse-driven protocol for the communication with the environment. The correctness of the system highly depends on the delays of the internal gates and the environment. The verification has been carried out by combining the core verification algorithm outlined above, together with the use of assume-guarantee reasoning [Pnu84] to perform a hierarchical verification by means of abstractions [Mel88], and the use of mathematical induction to prove the correctness of infinite-state systems. As a result, it has been proved the correctness of an IPCMOS pipeline regardless of the number of stages that conform it [PCSP02].

The key features of the presented work on the verification of timed systems can be summarized by the following topics:

- The use of relative timing allows to avoid the computation of the exact timed state space of the system, which is a common practice of model checking methods for timed systems. Instead in the proposed approach, the timed behavior of events is captured by means of partial orders that represent simple facts as if an event happens before another, *i.e.* relative temporal relations.

- As a consequence of the previous topic, the state space of the system can be represented and managed using symbolic methods with proved efficiency such as BDDs. This allows a natural extension of traditional symbolic model checking techniques for untimed systems into the timed systems domain of application.

- No global timing analysis is done for the whole system. Instead, the timing analysis is performed locally for a set of failure traces that are covered by a marked graph. Therefore, only a subset of the events of the system is involved and the timing analysis can be carried out very efficiently.

- Although timed systems provide delays for all the events in the system, often many of the constraints imposed by such delays are not required for the correctness of

the system. Because of the iterative nature of the proposed verification approach, timing information is only considered in an *on-demand* basis, as long as it is required to prove the infeasibility in the timed domain of a set of failure traces.

- As a result of the previous topic, the untimed state space of the system is refined incrementally as long as new timing information is taken into account. This incremental nature of the approach provides a good way to obtain at least partial results even on systems for which complete solutions could be too complex to compute.

- The proposed verification approach not only proves or disproves the correctness of the system with respect to a set of properties. If the system is correct the algorithm provides the set of relative timing relations used for the proof. Those relations constitute a set of sufficient timing constraints that guarantee the correctness of the system. On the other hand, if the system is incorrect, a counterexample failure trace is provided. The most important aspect of all this feedback is that can be used as valuable back-annotation information along a design process.

- The verification approach has been fully implemented into the CAV tool TRANSYT. The tool has proved its functionality as well as the validity of the overall verification approach, by verifying a set of different types of timed asynchronous circuits with up to more than 10<sup>6</sup> untimed states.

- Compositional verification methods have been combined with our basic verification approach in order to tackle the size/complexity issues involved in the verification of complex timed systems. Thus, abstractions, assume-guarantee reasoning and mathematical induction have been used to prove the correctness of a scalable pipelined architecture.

#### 1.6 Structure of the thesis

The rest of this document is organized as follows.

Chapter 2 introduces the fundamentals of the different formal models used in the subsequent chapters. Models such as Petri nets and several types of transition systems are described, together with some of their basic properties.

Chapter 3 introduces general background on the formal verification of timed systems and reviews the significant previous work on this area of research. Special attention is paid to the verification using timed automata, since the currently most successful methods and tools are based on them.

In Chapter 4 the main theoretical aspects of the relative timing-based verification approach for timed system, presented in this thesis are introduced. Examples of the applicability of the developed methodology are shown in Chapter 5, where different flavors of asynchronous circuits are verified. Chapter 6 presents a complex case study in which

1.6 Structure of the thesis 15

the basic verification approach is combined with assume-guarantee reasoning by means of abstractions, and mathematical induction. The result is the successful verification the IPCMOS architecture.

Chapter 7 summarizes the conclusions and contributions of this work and outlines some open areas for future research.

Additionally, some appendixes are included.

First, Appendix A analyzes the problem of determining the time separation between the events of a system. An algorithm for timing analysis on acyclic graphs is described in detail

Then, Appendix B provides implementation details of one of the key parts of the verification methodology.

And finally, Appendix C introduces the commands in the TRANSYT tool related to the verification of timed systems, which implement the presented verification approach.

# MODELS FOR CONCURRENT SYSTEMS

The best material model of a cat is another, or preferably the same, cat.

—Arturo Rosenblueth - Philosophy of Science, 1945

A theory has only the alternative of being right or wrong. A model has a third possibility: it may be right, but irrelevant.

—Manfred Eigen - The Physicist's Conception of Nature, 1973

# Summary

This chapter introduces the fundamentals of the models used for the specification, synthesis and verification of systems in the subsequent chapters. In particular, transition systems and Petri nets are introduced as models for untimed systems. Other classes of transition systems, such as timed transition systems and lazy transition systems are introduced as the models used for timed systems.

Transition systems and Petri nets provide an abstract view of the events and states of a system, without considering any binary encoding. In some cases, such as for the logic synthesis of circuits, or simply in order to achieve efficient implementations of verification algorithms, such encoding is required. The encoding allows the symbolic manipulation of a system using compact representations and efficient algorithms based on BDDs, for example. Chapter 5 provides details on the binary encoding of transition systems.

### 2.1 Introduction

As it will be seen in Chapter 4, the proposed verification approach uses timed transition systems to model the timed systems under verification. The approach, however, does not manipulate the exact timed state space of the system. Instead, the untimed state space, modeled by a transition system, is used as the starting point of the verification approach. Then, an incremental refinement of the untimed state space with relative timing information is carried out, thus leading to the use of lazy transitions systems. This chapter presents the fundamental concepts and notation related to the different types of transition systems involved in the verification approach.

On the other hand, *Petri nets* and its interpretation as *signal transition graphs* are often used to model asynchronous digital circuits and other concurrent systems. As a consequence, a number of verification methods have been developed under such formalisms (see Section 3.6). Moreover, in Chapter 5 some illustrative examples of the verification of timed systems are presented, which are originally specified with *Petri nets* and *signal transition graphs*. For this reason, we have considered appropriate to introduce the fundamentals of such modeling formalisms at the end of this chapter.

# 2.2 Transition systems

Transition systems (TS) are a formalism used to describe systems of concurrent processes [Arn94]. The formalism, although mathematically simple, can model most of the properties of such systems, and so can be used to study their semantics. Several theoretical tools based on transition systems have been developed, including equivalence relations with other formalisms (formal languages, Petri nets, etc.). The usefulness of these theoretical tools is supported by the existence of a variety of software tools.

Intuitively, a *transition system* consists of the set of possible states of a system, and a set of transitions that the system can produce in order to change from one state to another. In comparison to event-based models such as Petri nets, transition systems offer a view of a system at a lower level of abstraction.

#### DEFINITION 2.1 (TRANSITION SYSTEM)

A transition system (TS) [NRT92] is a quadruple  $A = \langle S, \Sigma, T, s_0 \rangle$ , where S is a non-empty set of states,  $\Sigma$  is a non-empty alphabet of events,  $T \subseteq S \times \Sigma \times S$  is a transition relation, and  $s_0$  is the initial state.

The elements of T are called transitions and are indistinctly denoted by  $s \stackrel{e}{\longrightarrow} s'$  or by (s, e, s').

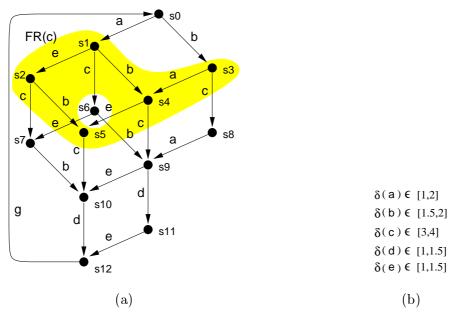

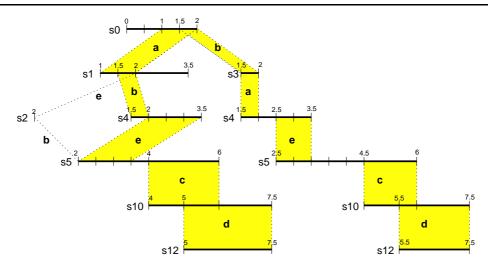

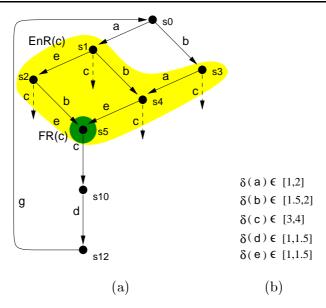

An event e is enabled at state s if  $\exists$  s  $\stackrel{e}{\longrightarrow}$  s'  $\in$  T. We will denote by  $\mathcal{E}(s)$  the set of events enabled at state s. The firing region of event e is defined as  $\mathsf{FR}(e) = \{ \mathsf{s} \in S \mid \mathsf{e} \in \mathcal{E}(\mathsf{s}) \}$ , i.e. the set of states where e is enabled.

2.2 Transition systems 19

Figure 2.1 An example of transition system.

A TS is finite if S and  $\Sigma$  are finite. A TS is called deterministic if for each state s and each event e there is at most one state s' such that  $s \stackrel{e}{\longrightarrow} s'$ . In the sequel, only finite transition systems will be considered. Moreover, no multiple arcs should exist between any pair of states, i.e.  $s \stackrel{e}{\longrightarrow} s' \in T \land s \stackrel{e'}{\longrightarrow} s' \in T \implies e = e'$ .

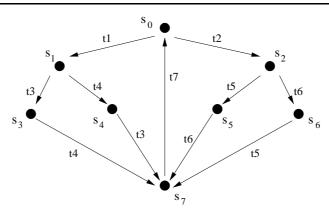

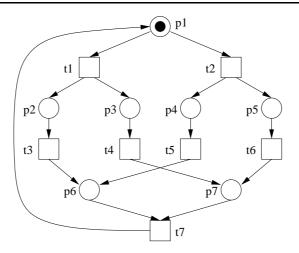

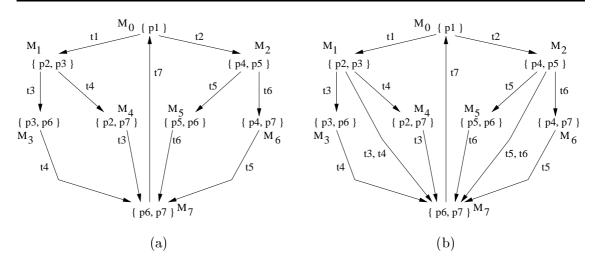

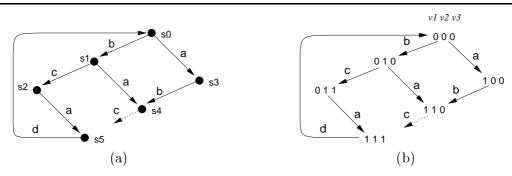

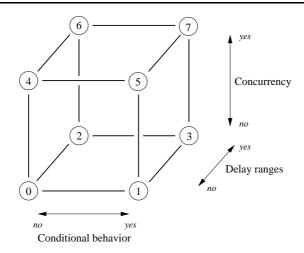

**EXAMPLE 2.1** A TS can be represented by an arc-labeled directed graph. A simple example of a TS is shown in Figure 2.1. States are represented as dots, transitions are the directed arcs between the states, and the events are the labels of the transitions. That is,  $S = \{s_0, \ldots, s_7\}, \ \Sigma = \{t_1, \ldots, t_7\} \ \text{and} \ T = \{s_0 \xrightarrow{t_1} s_1, s_1 \xrightarrow{t_4} s_4, \ldots\}.$  As an example, the firing region of event  $t_5$  is  $\mathsf{FR}(t_5) = \{s_2, s_6\}.$

**2**.1

#### DEFINITION 2.2 (RUN)

A run of a transition system  $A = \langle S, \Sigma, T, \mathsf{s}_0 \rangle$  is a sequence of transitions  $\rho = \mathsf{s}_1 \xrightarrow{\mathsf{e}_1} \mathsf{s}_2 \xrightarrow{\mathsf{e}_2} \cdots$ , such that  $\mathsf{s}_1 = \mathsf{s}_0$  and  $\forall i \geq 1 : \mathsf{s}_i \xrightarrow{\mathsf{e}_i} \mathsf{s}_{i+1} \in T$ . Event  $\mathsf{e}_i$  is said to fire at step i of the run.

With an abuse of notation, the expressions  $s_i \in \rho$ ,  $s_i \xrightarrow{e_i} s_{i+1} \in \rho$ ,  $s_i \xrightarrow{e_i} \in \rho$ ,  $\xrightarrow{e_i} s_{i+1} \in \rho$ , etc, will be often used to denote the fact that different fragments of a sequence belong to a run.

Several ordering relations between the events of a TS can be defined.

#### DEFINITION 2.3 (TRIGGERING, CONFLICT, CONCURRENCY)

Given a transition system  $A = \langle S, \Sigma, T, s_0 \rangle$  and two events  $e_1, e_2 \in \Sigma$ :

(a)  $e_1$  triggers  $e_2$  if the firing of  $e_1$  enables  $e_2$ , i.e. if  $\exists s_1 \xrightarrow{e_1} s_2 \in T$ , such that  $s_1 \notin FR(e_2)$  and  $s_2 \in FR(e_2)$ .

- (b)  $e_1$  disables  $e_2$  if  $\exists s_1 \xrightarrow{e_1} s_2 \in T$ , such that  $s_1 \in FR(e_2)$  and  $s_2 \notin FR(e_2)$ .  $e_1$  and  $e_2$  are in conflict if either  $e_1$  disables  $e_2$  or  $e_2$  disables  $e_1$ .

- (c)  $e_1$  and  $e_2$  are concurrent if there is a state in which both events are enabled and the firing of one of them does not disable the other:  $\exists s \in FR(e_1) \cap FR(e_2)$  :  $s \xrightarrow{e_1} s_1 \in T \land s \xrightarrow{e_2} s_2 \in T \Rightarrow \exists s_3 \in S : s_1 \xrightarrow{e_2} s_3 \in T \land s_2 \xrightarrow{e_1} s_3 \in T$ .

The following definition captures the notion of enabling of an event at a given state of a run, and the conditions for such event to keep enabled along the run until it fires or is disabled by the firing of another event.

### DEFINITION 2.4 (ENABLING INTERVAL)

Let  $A = \langle S, \Sigma, T, \mathsf{s}_0 \rangle$  be a TS and let  $\rho = \mathsf{s}_1 \xrightarrow{\mathsf{e}_1} \mathsf{s}_2 \xrightarrow{\mathsf{e}_2} \cdots$  be a run of A. Given an event  $\mathsf{e}$  and a state  $\mathsf{s}_i \in \rho$  such that  $\mathsf{s}_i \in \mathsf{FR}(\mathsf{e})$ , FirstEnabled $(\rho, \mathsf{s}_i, \mathsf{e})$  is defined as the state  $\mathsf{s}_j$ ,  $j \leq i$ , such that:

- $\bullet$   $j \leq k \leq i \Rightarrow s_k \in FR(e)$  (e is continuously enabled between  $s_j$  and  $s_i$ )

- $j > 0 \implies s_{j-1} \notin FR(e)$  ( e is not enabled before  $s_j$ )