A thesis presented for the degree of **Doctor of Philosophy**

### Algorithms and Methodologies for Interconnect Reliability Analysis of Integrated Circuits

#### Palkesh Jain

Advisor: Prof. Jordi Cortadella Computer Science Department, Universitat Politècnica de Catalunya

Co-Advisor: Prof. Sachin S. Sapatnekar

Department of Electrical and Computer Engineering,

University of Minnesota

Barcelona, Spain, 2017.

$\textcircled{\text{C}}$  2017, by Palkesh Jain ALL RIGHTS RESERVED

## Abstract

The phenomenal progress of computing devices – from room-sized machines of 1940's to literally invisible cloud based applications, has been made possible, largely by the sustained efforts of semiconductor industry in innovating techniques for packing increasing amounts of computational circuitry into smaller and denser microchips. Indeed, gigantically-integrated-circuits today contain billions of closely-packed transistors and possibly multi-billion interconnects which enables these tiny transistors to talk to each other (needless to mention, at Gigahertz+ frequency) – all in a space of few mm<sup>2</sup>.

Such aggressively downscaled discrete-IC-components (transistors and interconnects) silently suffer from increasing electric fields and impurities/defects during manufacturing. Compounded by the Gigahertz switching, the challenges of reliability and design integrity remains very much alive for chip designers, with Electromigration (EM) being the foremost interconnect reliability challenge.

Traditionally, EM containment revolves around three aspects, first of which is generation of EM guidelines at single-component level, whose non-compliance means that the component fails. Failure usually refers to deformation due to EM – manifested in form of resistance increase, which is unacceptable from circuit performance point of view. Second aspect deals with correct-by-construct design of the chip and lastly, it is about the final verification of EM reliability of taping-out silicon. Interestingly, chip designs today have reached a dilemma point of reduced margin between the actual and reliably-allowed current densities, versus, comparatively scarce system-failures. Consequently, this research is focussed on improved algorithms and methodologies for interconnect reliability analysis enabling accurate and design-specific interpretation of EM events.

In the first part, we present a new methodology for correct-by-construct design and verification of logic-IP (cell) internal EM verification: an inadequately attended area in the literature, unlike its counterparts in form of cell-external (signal) or power network EM. Our SPICE-correlated model helps in evaluating the cell lifetime under any arbitrary reliability specification or operating conditions, without generating additional data – unlike the traditional approaches. The model is apt for today's fab less eco-system, where there is a) increasing reuse of standard cells optimized for one market condition to another (e.g., wireless to automotive), as well as b) increasing 3rd party content on the chip requiring a rigorous sign-off. We present results from a 28nm production setup, demonstrating significant violations relaxation and flexibility to allow runtime-

level reliability retargeting.

Subsequently, we focus on an important aspect of connecting the individual component-level failures to that of the system failure. We note that existing EM methodologies are based on serial reliability assumption, which deems the entire system to fail as soon as the first component in the system fails. With a highly redundant circuit topology – that of a clock grid – in perspective, we present algorithms for EM assessment, which allow us to incorporate and quantify the benefit from system redundancies. With the skew metric of clock-grid as a failure criterion, we demonstrate that unless such incorporations are done, chip lifetimes are underestimated by over 2x.

This component-to-system reliability bridge is further extended through an extreme order statistics based approach, wherein, we demonstrate that system failures can be approximated reasonably by an asymptotic k-th component failure model, otherwise requiring costly Monte Carlo simulations. Using such approach, we can efficiently predict a system-criterion based time to failure (TTF) within existing EDA frameworks based on component level verification.

The last part of the research is related to incorporating the impact of global/local process variation on current densities as well as fundamental physical factors on EM TTF. Through Hermite polynomial chaos based approach, we arrive at novel variations-aware current density models, which demonstrate significant margins (> 30%) in EM lifetime when compared with the traditional worst case approach.

The above research problems have been motivated by the decade-long work experience of the author dealing with reliability issues in industrial SoCs, first at Texas Instruments and later at Qualcomm. At TI, he led the Reliability CAD team with the charter of solving reliability issues for TI's various worldwide businesses including ASICs, DSP, Wireless and Automotives. Some of the related work which he published earlier is listed as: [JJ12, JCPA14, PJK10, Jai07].

## Acknowledgement

This journey towards obtaining a doctoral degree, after more than a decade of professional career, wouldn't have been possible without the help, support and inspiration from a lot of different people in my life. I am grateful to be able to acknowledge their contributions here.

First and foremost, I have been fortunate enough to be guided by not one, but two thesis advisors: Professors Sachin S. Sapatnekar and Jordi Cortadella. Although a remotely done PhD, in no means has it been less rigorous than a fulltime one: with around a thousand email exchanges, and, each email warranting a high quality and meticulously thought-through response. Its indeed a privilege to get such mindshare, and, tremendous amount of patience for my writing from Sachin. His insights, insistence on simplicity of thoughts, focus on details and constant drive for precision have ensured the quality output, and, forced me to think harder about the problems and their solutions. He has been an exceptional personal mentor as well, investing a great deal of time in several emails on overseeing my general professional well-being too. Ofcourse, Sachin sets incredibly high standards of operating oneself personally and professionally. Even though it was testing on few occassions in the course of PhD, today, I truly appreciate and will consider myself accomplished to even emulate a small bit of that in my life. Thanks Sachin, for giving me this opportunity and guiding me through the very end.

The other half of the gratitude goes to Jordi. He gave me complete freedom to choose the problems and has been extremely accommodating on the part time research arrangement. I have benefitted greatly from Jordi's focus on big picture (beyond interconnects) and his uncanny system level expertise. Besides keeping an eye on the thesis progress, he was always available to help with any issues I faced, and was very prompt with feedback on the various drafts that I sent. Jordi, Sachin, working with both of you has been an honour and I look forward to our future collaborations. Thanks are also due to the research committee members and reviewers for their feedback. From the research group, would like specially thank Vivek Mishra for all the enriching brainstorming we did.

This thesis has been primarily motivated by the live reliability problems faced in industry, based on my work experience – first with Texas Instruments and later with Qualcomm. I want to express my gratitude to my colleagues, friends and management at Texas Instruments: Guru Prasad, Suravi Bhowmik, Subash Chander, Arvind NV, Gaurav Varshney, Jay Ondrusek, Vijay Reddy, Srikanth Krishnan, Anand Krishnan and Rob Baumann. Indeed, the exciting reliability journey in TI only stemmed from discussions with Frank Cano and Hugh Mair, and, my thoughts on EM wouldn't have started but for the great conversations with Young-Joon Park and Ki-Don Lee. At Qualcomm, I have been fortunate to have extremely supportive management and

must thank Venugopal Puvvada, Esin Terzioglu, Manoj Mehrotra and Rajagopal Narayanan.

Back to where it all started, I appreciate my professors at IIT Bombay who introduced me to the fascinating field of semiconductors. In particular, I'll forever remain indebted to Prof. J. Vasi for cultivating the required mindset.

Undoubtedly, work and research wouldn't have been possible without the calm and joyful backdrop which my family and friends in Bangalore, Indore and Hazaribagh provided. Can't thank them enough! Specifically to Coral - who more as friend helped on the philosophical aspects of the 'doctor of philosophy', and above all to my Mom for her unconditional love and blessings.

If there is one discernible change which has happened over the course of PhD, it is turning of our little princess, Kopal, from cuddly age of two years to that of bubbling five! Ever since she has been in my life, every day has been special. Her laughter and being around has made writing this thesis a very pleasant exercise. Lastly, words fall short in thanking my loving wife Kuhu, for her patience with me throughout the course of my doctoral work. I'm truly fortunate to have her boundless love and calm nature by my side. Undeniably, its her and Kopal, who have sacrificed the most in forms of the countless weekends, festivals and holidays over which this part-time research was primarily done and I can only promise to make up for the time gone!

When there are so many people to thank, one should thank the almighty ... here I do, for giving me such wonderful friends, colleagues, teachers and family!

Palkesh

To my Dad ... who has been the inspiration behind this, and, to Kopal ... who has been the motivation to finish this (soon!)

## Contents

| A            | bstra | et :                                                                  | iii |

|--------------|-------|-----------------------------------------------------------------------|-----|

| $\mathbf{C}$ | onten | ts                                                                    | iii |

| Li           | st of | Figures                                                               | xi  |

| Li           | st of | Algorithms                                                            | ζV  |

| Li           | st of | Tables x                                                              | vi  |

| 1            | Intr  | oduction                                                              | 1   |

|              | 1.1   | Motivation                                                            | 1   |

|              | 1.2   | Existing Approaches for Electromigration                              | 3   |

|              |       | 1.2.1 Current Computation                                             | 4   |

|              |       | 1.2.2 Current Density Target (Thresholds) Computation                 | 5   |

|              | 1.3   | Limitations of Prior Art                                              | 7   |

|              | 1.4   | Thesis Objectives                                                     | 8   |

|              | 1.5   | Organization                                                          | 9   |

| 2            | Bac   | ground                                                                | 11  |

|              | 2.1   | Electromigration basics                                               | 11  |

|              |       | 2.1.1 Alternative Electromigration Modeling Paradigms                 | 13  |

|              |       | 2.1.2 Electromigration under Bipolar (AC) Currents                    | 15  |

|              |       | 2.1.3 $$ Accelerated Electromigration Under Wire Joule Heating . $$ . | 16  |

|              |       | <i>y</i> 11                                                           | 17  |

|              | 2.2   | EM Reliability Mathematics                                            | 18  |

|              |       | 2.2.1 TTF Distribution: Lognormal                                     | 18  |

|              |       | F                                                                     | 19  |

|              | 2.3   | Monte Carlo random sampling approach                                  | 19  |

|              | 2.4   | Clock grids: introduction and previous EM checking methods $$ . $$    | 19  |

|              | 2.5   | Electromigration in power grids: introduction and previous ap-        |     |

|              |       | proaches                                                              | 20  |

|              | 2.6   | Conclusions                                                           | 21  |

| 3 | Log  | ic IP-Internal Electromigration Assessment Methodology         | 22        |

|---|------|----------------------------------------------------------------|-----------|

|   | 3.1  | Introduction                                                   | 22        |

|   | 3.2  | EM Modeling: Basic Framework Under Purely Capacitive Loads     | 25        |

|   |      | 3.2.1 Electromigration Basics: Recap                           | 25        |

|   |      | 3.2.2 Traditional Approach for Modeling EM Reliability         | 26        |

|   | 3.3  | Addressing L1: Incorporating Arbitrary Switching And Clock     |           |

|   |      | Gating In Frequency Estimation                                 | 27        |

|   |      | 3.3.1 Library Level Current Characterization                   | 27        |

|   |      | 3.3.2 Effective Current Estimation for a Chip-Level Instance   | 28        |

|   |      | 3.3.3 Instance Safe Frequency Estimation at Chip Level         | 32        |

|   | 3.4  | Addressing L2: Modeling The Impact Of Arbitrary RC Loading.    | 34        |

|   |      | 3.4.1 Overview of Prior Work                                   | 34        |

|   |      | 3.4.2 Prior Work: Limitations                                  | 35        |

|   |      | 3.4.3 Proposed Solution: RC Loading and $C_{in}$ Modeling      | 36        |

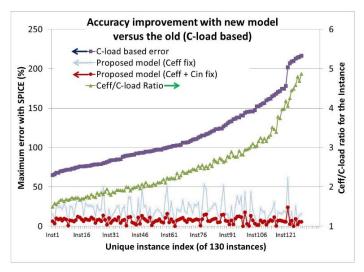

|   |      | 3.4.4 RC Loading and Cin Model Validation: Results             | 38        |

|   | 3.5  | Addressing L3: On-The-Fly Retargeting of Reliability For Arbi- |           |

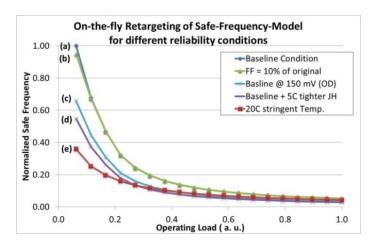

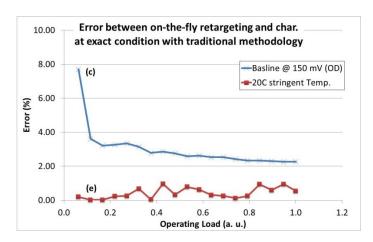

|   |      | trary Specifications                                           | 41        |

|   |      | 3.5.1 Case Studies Incorporating Reliability Retargeting       | 42        |

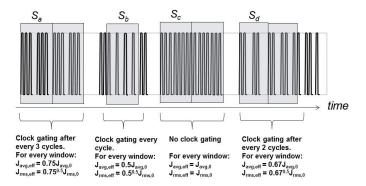

|   |      | 3.5.2 Incorporating Non-uniform Clock Gating                   | 45        |

|   | 3.6  | Addressing L4: Accelerated Data Generating Using Cell Response |           |

|   |      | Modeling                                                       | 47        |

|   | 3.7  | Production Design Analysis                                     | 50        |

|   | ٠    | 3.7.1 Library Characterization                                 | 51        |

|   |      | 3.7.2 Final Reliability Verification                           | 51        |

|   | 3.8  | Conclusion                                                     | 54        |

| 4 | Sto  | chastic and Topologically Aware Electromigration Assess-       |           |

|   |      | nt Methodology                                                 | <b>55</b> |

|   | 4.1  | Introduction                                                   | 55        |

|   | 4.2  | Analytical Approach for Systems With Redundancy                | 57        |

|   |      | 4.2.1 Basics of Electromigration                               | 57        |

|   |      | 4.2.2 Reliability Calculations for Changing Stress             | 57        |

|   |      | 4.2.3 Reliability Calculations for System with Redundancy      | 60        |

|   | 4.3  | Monte Carlo Framework for System Reliability Estimation        | 61        |

|   |      | 4.3.1 Monte Carlo Framework Based Clock Buffer Reliability     |           |

|   |      | Analysis                                                       | 63        |

|   |      | 4.3.2 Monte Carlo Framework Based Analysis of Buffers in Re-   |           |

|   |      | dundant Configuration                                          | 65        |

|   | 4.4  | Clock Skew Estimation                                          | 65        |

|   | 4.5  | Conclusion                                                     | 67        |

| 5 | Fast | t Stochastic Analysis of Electromigration in Power Distri-     |           |

|   |      | ion Networks                                                   | 69        |

|   | 5.1  | Circuit-level electromigration verification                    | 69        |

|   | 5.2  | Limitations of existing EM methodologies                       | 71        |

|   |      | 5.2.1 Statistical variations in $J$                            | 71        |

|              |        | 5.2.2  | Outline of the proposed methodology                  | . 73 |

|--------------|--------|--------|------------------------------------------------------|------|

|              | 5.3    | Model  | ing EM and wire currents                             | . 75 |

|              |        | 5.3.1  | TTF modeling                                         | . 75 |

|              |        | 5.3.2  | Evaluating the PDN                                   | . 76 |

|              |        | 5.3.3  | Modeling the distributions of wire current densities | . 77 |

|              | 5.4    | Model  | ing wire current variation                           | . 79 |

|              |        | 5.4.1  | Hermite PC based model                               | . 80 |

|              |        | 5.4.2  | Hermite PC: Coefficient estimation                   | . 81 |

|              |        | 5.4.3  | Relevance to alternative EM checking paradigms       | . 82 |

|              | 5.5    | EM U   | nder circuit redundancy                              | . 83 |

|              | 5.6    | Result | S                                                    |      |

|              |        | 5.6.1  | Statistical Variability Estimation                   |      |

|              |        | 5.6.2  | Application of Order Statistics                      |      |

|              | 5.7    | Conclu | sion                                                 | . 94 |

| 6            | Con    | clusio | ns                                                   | 95   |

| В            | ibliog | graphy |                                                      | 97   |

| ${f L}$ i    | ist of | Public | cations                                              | 106  |

| $\mathbf{A}$ | bout   | the A  | uthor                                                | 107  |

# List of Figures

| 1.1 | Variation of EM capability (allowed current density) across various markets                                                                                                                                                                                                                                                                         | 3  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Basic Electromigration process and Electromigration in signals, power-network and cell-internal                                                                                                                                                                                                                                                     | 3  |

| 1.3 | Spectrum of cell-internal EM modeling. a) Circuit schematic highlighting the problem space. b) Representative f-L modeling [JJ12]. c) EM model captured in standard liberty syntax [Lib16]. d) Model used in some of the industrial designs [SKK14]                                                                                                 | 5  |

| 1.4 | A representative design cycle in a typical semiconductor house: starting from obtaining reliability specifications, to standard cell library design to obtaining a final design database. Adapted from Bickford <i>et al.</i> [BB13]                                                                                                                | 6  |

| 2.1 | A typical triple point in a wire                                                                                                                                                                                                                                                                                                                    | 11 |

| 2.2 | Voiding and extrusion in Copper metal lines during Electromigration [Lee13]                                                                                                                                                                                                                                                                         | 12 |

| 2.3 | a) As the incoming and outgoing atomic flux are the same, the atomic flux divergence along the interconnect is zero, resulting in no EM damage b) Lead Y carries half current density of lead X but fails faster than lead X, contrary to the conventional EM expectation. The via-node vector EM method catches this using flux divergence [PJK10] | 15 |

| 2.4 | The via-node method compares the effective current density of a via node with the current density thresholds while the conventional method compares the current density. The via-nodes are most susceptible to the EM failures and the effective current density should be smaller than the thresholds. [PJK10]                                     | 15 |

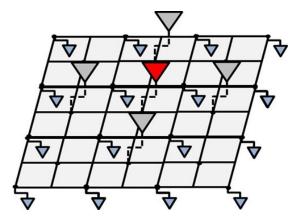

| 2.5 | Representative clock grid, highlighting the redundant source-sink paths and the multiply driven system.                                                                                                                                                                                                                                             | 20 |

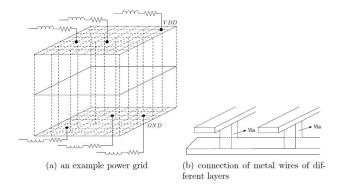

| 2.6 | A typical power grid representation in modern SoC [Yu14]. $$                                                                                                                                                                                                                                                                                        | 21 |

|     |                                                                                                                                                                                                                                                                                                                                                     |    |

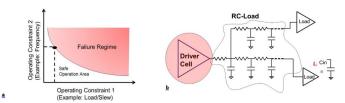

| 3.1        | a) Traditional approach for EM verification using the safe operating region concept. b) Schematic highlighting the EM-critical cell, driving an RC load network (visvis safe frequency obtained for pure C load) | 24 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

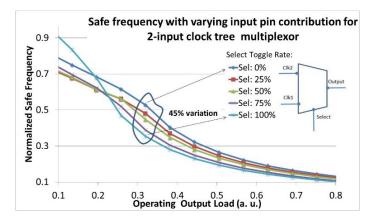

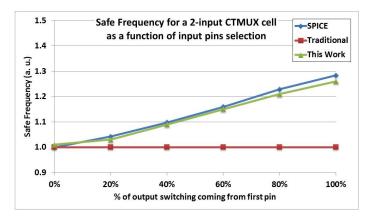

| 3.2        | $f_{safe}$ plot for a 2-input clock-multiplexor cell. Both input clocks switch at 100%, while the select pin chooses one of them, with                                                                           |    |

| 3.3        | varying likelihoods                                                                                                                                                                                              | 26 |

| 3.4        | current characterization                                                                                                                                                                                         | 29 |

| 3.5        | a cell                                                                                                                                                                                                           | 33 |

|            |                                                                                                                                                                                                                  | 34 |

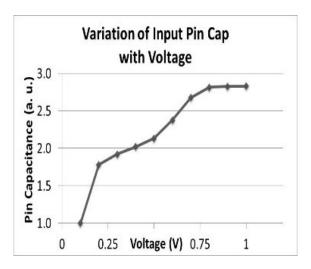

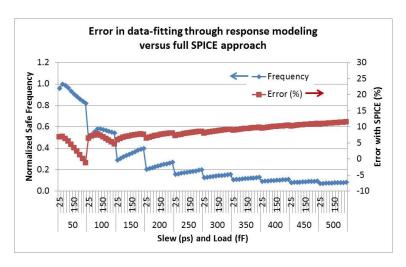

| 3.6<br>3.7 | Variation of the input pin cap with voltage                                                                                                                                                                      | 39 |

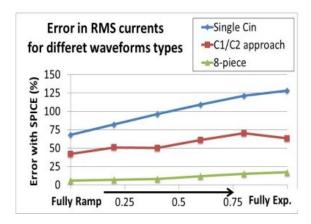

| 3.8        | ramp to fully exponential)                                                                                                                                                                                       | 39 |

| 3.9        | Ceff/C-load ratio) at the design level                                                                                                                                                                           | 40 |

| 3.10       | fixed slew point)                                                                                                                                                                                                | 44 |

| 3.11       | ditions, (c) and (e), of Fig. 3.7                                                                                                                                                                                | 45 |

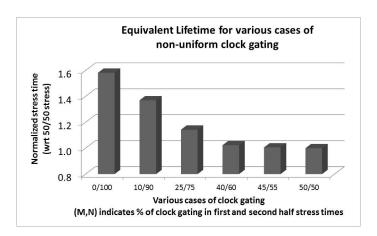

| 3.12       | sponding $J_{avg}$ , $J_{rms}$ )                                                                                                                                                                                 | 46 |

| 3.13       | in first half and second half of the stress time                                                                                                                                                                 | 47 |

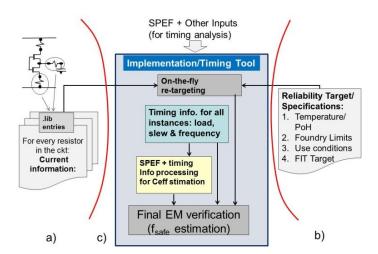

| 3.14       | SPICE (red). fsafe obtained through response modeling (blue) Overall methodology and data-flow diagram for the proposed                                                                                          | 50 |

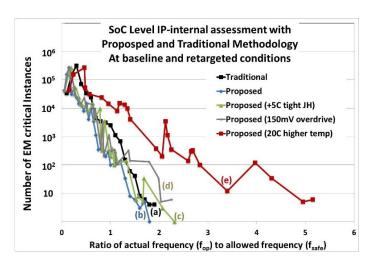

| 3.15       | method                                                                                                                                                                                                           | 52 |

|            | ity condition analysis with proposed methodology                                                                                                                                                                 | 53 |

| 4.1        | A one-level clock grid schematic showing several buffers arranged in redundant configuration                                                                                                                     | 56 |

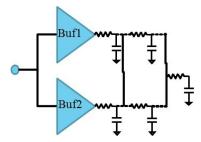

| 4.2  | A single stage of the clock grid with multiple buffers driving the                                                                                                                                                                                                                                                    |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | wire segments                                                                                                                                                                                                                                                                                                         | 57 |

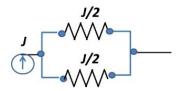

| 4.3  | Schematic showing a parallel two-component system                                                                                                                                                                                                                                                                     | 58 |

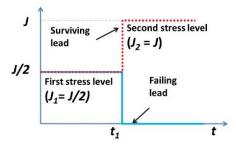

| 4.4  | Current profile evolution, with first failure occurring at time $t_1$                                                                                                                                                                                                                                                 | 58 |

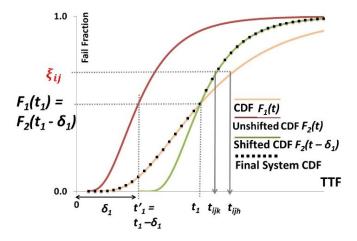

| 4.5  | Analytically estimated CDF evolution of a single component when it undergoes a stress change. The dotted line is the effective CDF,                                                                                                                                                                                   | 59 |

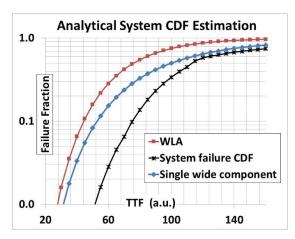

| 4.6  | when stress change occurs at t1                                                                                                                                                                                                                                                                                       | 61 |

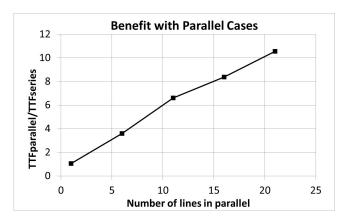

| 4.7  | Showcasing the increasing benefit of redundancy with the number of components arranged in parallel configuration                                                                                                                                                                                                      | 62 |

| 4.8  | A simple high-drive (32x) buffer driving lumped load. Shown are Vdd, Vss, input and output resistors (sites for EM), analyzed                                                                                                                                                                                         |    |

|      | stochastically                                                                                                                                                                                                                                                                                                        | 64 |

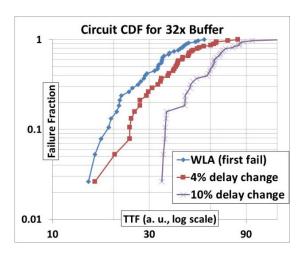

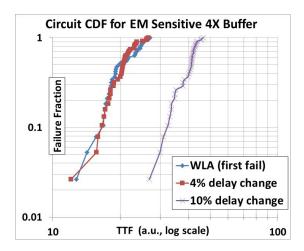

| 4.9  | Circuit CDF showing the failure rate evolution in a single 32x drive buffer circuit (of Fig. 4.8), driving lumped load                                                                                                                                                                                                | 64 |

|      | CDF for a low-drive 4x circuit, where circuit redundancies reduce, leading to an early delay-based EM failure                                                                                                                                                                                                         | 65 |

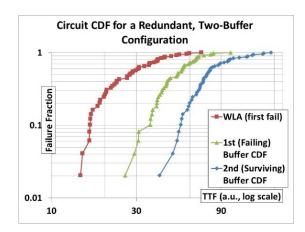

| 4.11 | CDF for a system with two buffers arranged in a redundant configuration (as in Fig. 4.2). Significant margin is shown between TTF and the failure of first buffer. Margin builds up with addi-                                                                                                                        |    |

|      | tion of one more redundant buffer                                                                                                                                                                                                                                                                                     | 66 |

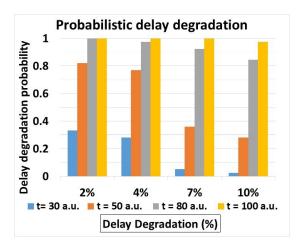

|      | Probabilistic delay degradation with time (column-cluster represent various times)                                                                                                                                                                                                                                    | 67 |

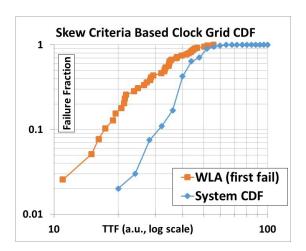

| 4.13 | Skew-criteria based CDF of the clock-grid. For a 10% FF, about 2X margin exists between WLA and skew-criteria based failures.                                                                                                                                                                                         | 68 |

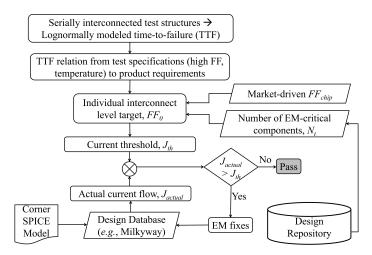

| 5.1  | A schematic of the traditional EM verification flow                                                                                                                                                                                                                                                                   | 70 |

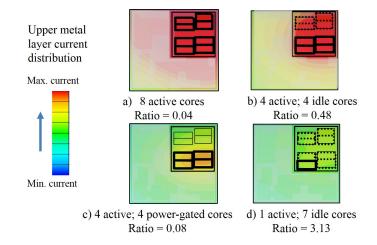

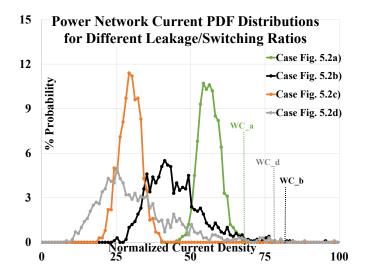

| 5.2  | An octacore SoC, with the eight CPUs shown on the upper right, under various workloads. Depending on whether the CPUs are in active, idle, or power-gated mode, the ratio of total active power to total leakage power may vary, and the nominal current in the power grid (shown by the contours) may show different |    |

|      | distributions                                                                                                                                                                                                                                                                                                         | 72 |

| 5.3  | Current density PDFs in a power network for various cases mapping to Fig. 5.2                                                                                                                                                                                                                                         | 72 |

| 5.4  | The proposed EM verification flow, where the highlighted regions indicate modifications to the traditional flow (Fig. 5.1)                                                                                                                                                                                            | 74 |

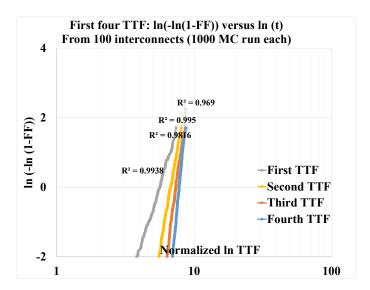

| 5.5  | Time to $k^{\rm th}$ failure on a Gumbel plot demonstrating applicability of order statistics                                                                                                                                                                                                                         | 85 |

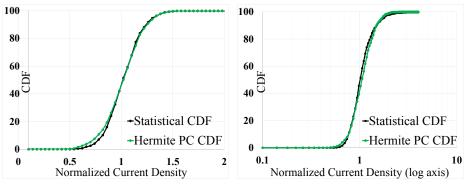

| 5.6  | Current density PDFs and CDFs derived through statistical SPICE simulations and Hermite PC based approach for Gaussian and                                                                                                                                                                                            |    |

|      | non-Gaussian cases                                                                                                                                                                                                                                                                                                    | 88 |

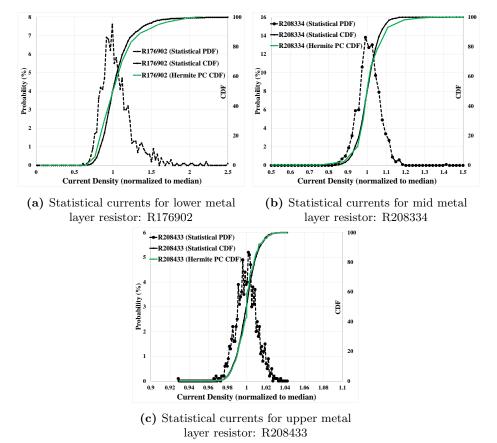

| 5.7  | Current density PDFs and CDFs derived through statistical SPICE     |    |

|------|---------------------------------------------------------------------|----|

|      | simulations and Hermite PC based approach for three resistor        |    |

|      | cases, corresponding to lower, mid and upper metal layers, incor-   |    |

|      | porating local variations. Distributions becomes narrower as the    |    |

|      | resistors move to upper metal layers                                | 89 |

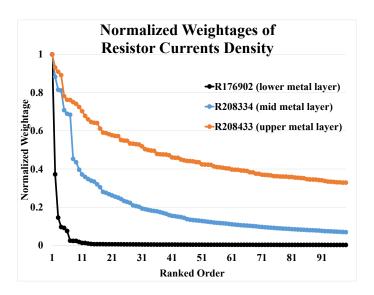

| 5.8  | Normalized and ranked-order sensitivity of different resistors to   |    |

|      | individual current sources. x-axis indicates the identifier for one |    |

|      | amongst several current-sources in the design                       | 90 |

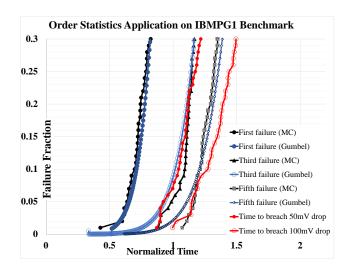

| 5.9  | Application of Order Statistics Based EM Prediction on PG bench-    |    |

|      | mark, IBMPG1                                                        | 92 |

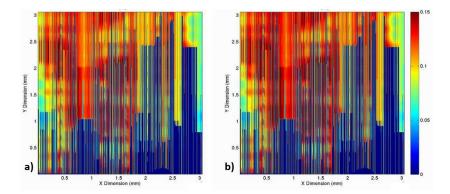

| 5.10 | Voltage drop maps of the power grid, IBMPGNEW1 (left) at            |    |

|      | t=0, showing the inherent IR drop of the circuit with no wire       |    |

|      | failures (right) after the circuit undergoes 20 EM events, after    |    |

|      | which there is at least one node whose voltage drop is 50mV         |    |

|      | higher as compared to its $t = 0$ value. The IR drop scale is       |    |

|      | described at right                                                  | 93 |

# List of Algorithms

| 3.1 | Current density computation through every resistor of a cell | 31 |

|-----|--------------------------------------------------------------|----|

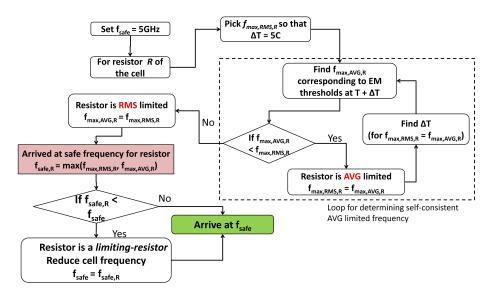

| 3.2 | Self-consistent safe frequency estimation of the cell        | 35 |

| 3.3 | Accurate EM verification considering RC loads                | 41 |

| 3.4 | Incorporating non-uniform clock gating                       | 48 |

| 4.1 | Monte Carlo based approach for stochastic EM analysis        | 63 |

## List of Tables

| 1.1 | Overall thesis contribution areas and comparison with prior art                                                                                                                                                                               | 9  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Runtime comparisons with proposed and traditional methods, for a single cell                                                                                                                                                                  | 50 |

| 3.2 | Overall comparison of traditional versus proposed methodology.<br>Traditional method was run only at baseline condition due to<br>runtime issues, whereas the proposed method could run at various                                            |    |

|     | reliability conditions                                                                                                                                                                                                                        | 53 |

| 5.1 | Comparison of our analytical EM lifetime prediction against a timing-based WC approach                                                                                                                                                        | 90 |

| 5.2 | Comparison of our analytical EM lifetime prediction against Monte Carlo and WC approach, performed on different power grid benchmarks. The failure criterion is $50 \text{mV}$ higher voltage drop on any node as compared to its $t=0$ value | 91 |

| 5.3 | Application of order model for threshold based verification of                                                                                                                                                                                | -  |

|     | circuits                                                                                                                                                                                                                                      | 94 |

## Chapter 1

### Introduction

#### 1.1 Motivation

Computing is an indispensable part of our lives today, including our working, industrial and government interactions. The devices which perform this computing have pushed their individual performance and the power envelopes to the edge, while their counts have already surpassed the number of human beings on the planet, and by 2020, such internet-connected devices are expected to number more than 50 billion [IOT15].

This impressively sustained-and-articulated improvement in computer hardware has been supported by significant innovation in various fields, a facet of which includes periodic doubling of transistor densities in integrated circuits over the past fifty years – a phrase more commonly known as Moore's law. However, the physics, and the economics of such doubling gets tricky by the collateral reduction in the transistor gate length and interconnect wire dimensions. For example, the gate length of the state-of-the-art active device is in the range of 20nm and the minimum pitch of metal wires is 54nm, [ITR15]. Moreover, not just scaling, but several other dimensions are required to be addressed to keep pace with the desired performance-power envelope, including novel transistors (FinFETs) [HLK+00], circuits, architecture (parallelized, bigLITTLE, etc. [Gre11, Gra03]), EDA methodologies, systems and softwares.

Such large scale integration of devices and interconnects come with significant challenges revolving around the timing analysis, physical design (thermal), power delivery challenges and voltage limits regulation/management. Consequently, due to conflicting requirement of increasing performance and lowering power, we see a) narrow interconnects with much higher current densities and b) transistors with rising electric fields and quantum effects such as discrete dopants and gate oxide traps. As a result, device reliability mechanisms have become pressing concern in scaled technologies. While transistors degrade temporally due to aging caused by effects like Negative Bias Temperature Instability (NBTI), Time Dependent Dielectric Breakdown (TDDB) and hot-carrier effects,

the interconnects also degrade due to various effects, including Electromigration (EM) and stress-migration, etc.

Undoubtedly, EM is the most prominent interconnect degradation mechanism and is the central topic of research for this work. While EM is difficult to accelerate in-house on real products, it is not very uncommon to relate and attribute the field failures directly to it. Indeed, a recent product recall by Intel 6-series chipset using 65 nm technology has been attributed to Electromigration, with the consistent failure signature being "aggressive data transfers over time causing more errors" [ELE11]. Such product recalls are obviously costly, sometimes in range of > \$1B, and therefore, any amount of investment upfront in designing better and robust ICs is much more economical.

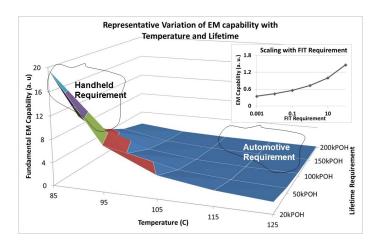

Electromigration is a process in which mass transport takes place as a result of interaction between the moving electrons and the metal atoms (for example Copper or Aluminium) at high current densities [Ori10]. Also, under identical conditions of geometry, current and temperature, the rate of EM degradation depends on the specific microstructure of the metal line/via. As a result, and due to random manufacturing variations, the time-to-failure is a random variable, which brings in the stochasticity into lifetime assessment. Generally, an EM-induced failure of a metal line (wire, or interconnect) is deemed when the line-resistance changes by over a specified magnitude (for example 10%), and usually there is an upper limit on the total number of such failed wires in the design, also known as the target failure-fraction (FF), which directly relates to the defective parts per million (DPPM). Additionally, EM degradation depends very strongly on the operating conditions - namely, temperature, voltage and the overall stress time, which, along with the expected failure-fraction, constitute the reliability specification. Such specification is fundamental for IC vendors, since it is sensitive to the end-market. For example, ICs going into the wireless handheld devices rarely push EM to its limit (due to lower operating temperatures and relaxed fail/lifetime requirements), while the ICs going into automotive or server applications demand very low failure rate from EM, and that too at the harsh conditions, as seen from Fig. 1.1.

Having said this, EM is an old field of study with a strong tradition, including theoretical analysis, failure models, and full-chip estimation/checking techniques. Specifically, its verification is broadly around:

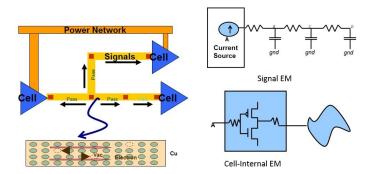

- Accurately computing the current densities in the individual wires of the chip. These wires are cell-external: signals and power nets connecting cells and cell-internal: wires within a logic-IP (standard cells) or mixed signal IP block, as seen in Fig. 1.2 [JJ12].

- Arriving at the current density targets for individual wires of a given chip. This involves careful understanding of the reliability specification, as well as the accounting of the individual wire geometry and surroundings. Additionally, while the EM reliability at component level is well specified by the foundries, it is the full chip level system reliability which gets specified to the chip designers, warranting some manipulations to derive

Figure 1.1: Variation of EM capability (allowed current density) across various markets.

component level targets. In short, the current targets are a function of: the system topology and the system level reliability requirements.

Figure 1.2: Basic Electromigration process and Electromigration in signals, power-network and cell-internal.

### 1.2 Existing Approaches for Electromigration

Revolving around the two themes discussed, the existing approaches for EM containment can be categorized as follows:

#### 1.2.1 Current Computation

#### Cell-External: Signal and Power Analysis

The current flow computation in the cell-external signal wires and power network is routinely performed through industrial EDA tools which perform the IR drop analysis [RED15, EDI15, mag14]. The power network currents are a collateral of the IR drop analysis, although, the vectors at which the currents get computed can get slightly changed. For signals, the current computation is slightly more involved as the RMS currents through the signal wires are a function of the current waveform. However, using timing-like techniques of asymptotic waveform estimation, such a problem is well managed and is an industry practice [JJ12]. The focus of signal EM has been majorly on the clock network due to high switching activity as compared to the data nets. Due to this, the physical routing of the clock distribution is almost always on the non-default routing. Indeed, a rich field of literature exists on accurate current computation for cell-external clock and power distribution network [TMS08, Raj08, BOZD03, Lie13, YWC+06].

#### Cell-Internal Analysis

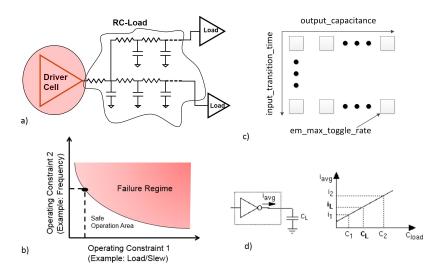

On the contrary, the current computation for wires within the standard cells (Fig. 1.3a) haven't seen an adequate amount of research. The lack of same has been often compensated by a pessimistic design of the standard cell library which have wider than required routes and track heights. However, with the technology and area shrinking, this overdesign turns unacceptable and indeed, there is a recent string of work on cell internal EM analysis [Dod15, US14]. For example, Vaidyanathan et al. [VLSP14] highlights a standard cell library design methodology in which only selective routes within the standard cell are widened and how the library architecture itself is EM-aware.

Since the EM reliability of a standard cell is a function of the output load and operating frequency, some industrial implementation tools [EDI15, mag14] use a precharacterized table that models the tradeoffs in operating load and frequency, as shown in Fig. 1.3b. The intuition behind such a table (frequency versus load; f-L) is simple: the current flow inside the standard cell increases with the operating load, and hence the frequency should be lowered to meet the reliability specification. In fact, in the standard liberty file syntax, such model has been documented in standard manner [Lib16] to be readily consumed by place and route tools (Fig. 1.3c). This model has been used at the chip level to determine the safe frequency (fsafe) of an instance for any design/reliability parameter, and then make corresponding design fixes [RLC16]. Needless to say, most of the EM-critical cells are the ones that operate at higher loads, frequencies or slews. Similar model (Fig. 1.3d) has been reported by Sharma et al. and used on industrial designs [SKK14].

A different perspective on cell-internal modeling was presented by Panda et al. [OHG<sup>+</sup>04] which entails pre-characterization of cell internal currents and using them for total failure rate projection. Burd et al. also presented an

Figure 1.3: Spectrum of cell-internal EM modeling. a) Circuit schematic highlighting the problem space. b) Representative f-L modeling [JJ12]. c) EM model captured in standard liberty syntax [Lib16]. d) Model used in some of the industrial designs [SKK14].

advanced and accurate current calculation methodology based on circuit tracing and computing the effective activity of every resistor in the circuit [BAK<sup>+</sup>13].

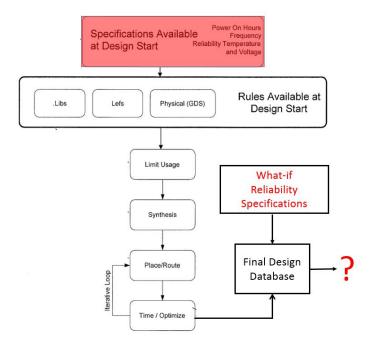

A live example of how the reliability specifications roll-into design process can be seen from Fig. 1.4, adapted from Bickford *et al.* [BB13]. As can be seen, the reliability specifications are primary to kick-start the library design process, which trickles down to the final design database.

#### Conditions for Current Computation

As the current flow in the interconnect comprises of the switching and leakage current together, it is a strong function of the semiconductor process strength and statistical process variations. However, the present industry practice is to typically assume strong transistor (which enforces sharp slopes: higher RMS currents as well as higher leakage) and interconnects with worst parasitic capacitances (which increases the charging cap.). Such guidance for corner are typically provided by semiconductor foundries in their reference flows [TSM16, GF16, ICF14].

#### 1.2.2 Current Density Target (Thresholds) Computation

Once the currents are computed appropriately, the next step is to verify the current against the guidance. Needless to say, these guidance, or specifications, become fundamental to design closure, as again inferred from Fig. 1.4, where the box highlighted in the red indicates the current density targets or thresholds.

Figure 1.4: A representative design cycle in a typical semiconductor house: starting from obtaining reliability specifications, to standard cell library design to obtaining a final design database. Adapted from Bickford *et al.* [BB13].

The thresholds, in turn, are a function of several design variables, as listed below:

#### **Topology Effects**

EM verification methodologies have to deal with the dilemma that while the experimental test structures from which the current density limits are derived are discrete in nature, those limits are applied on circuits which are far more complex than a single individual interconnect. However, traditionally, designers make a simplifying approximation, in which the system is treated as a serial system, making it weakest link approximated (WLA), wherein, a failure is deemed when the first component fails [FP89]. While this approximation simplifies the checking, it completely ignores the system topology.

#### System Design

Another important consideration while choosing the current density thresholds is the design style itself. Indeed, an important parameter on which system reliability depends is the number of components  $(N_t)$  which are running at or near thresholds. Using serial reliability assumption, we can actually relate the chip and component level reliability  $(FF_{chip})$  and  $FF_0$  respectively) for this case

$$FF_{chip} = 1 - (1 - FF_0)^{N_t} \implies FF_0 \approx FF_{chip}/N_t \tag{1.1}$$

Since  $N_t$  is a design knob with the chip designer, a power grid style having a smaller  $N_t$  implies that  $FF_0$  must be targeted  $\approx FF_{chip}$ . Alternatively, for higher  $N_t$  design style,  $FF_0$  must be mandated to be smaller than  $FF_{chip}$ ; usually 3 orders lower for typical power network comprising millions of resistors. In other words, a design which allows lots of wire to run near the current density thresholds must choose a smaller value of current threshold.

#### System Reliability Budget and Retargeting

Finally, the current thresholds are a strong function of the reliability requirements, namely: lifetime, joule heating criteria, temperature and the overall failure rate requirement. A relation in them is often provided by the foundries. However, as the semiconductor design houses explore newer markets for an already manufactured, functioning silicon, they are often forced to tradeoff the reliability variables [YTW14].

#### 1.3 Limitations of Prior Art

While above methodologies have worked reasonably well till so far, with advancing technology and convoluted circuit effects, it is becoming more and more inadequate in accurately predicting EM safety. Specifically, we highlight following limitations with the prior art:

- Cell-Internal EM Modeling: the prior arts discussed till so far suffer from the inability to incorporate the impact of parasitic wire loading on the cell and instead abstract the reliability as a function of lumped load. Further, it cannot incorporate dependency of arbitrary switching rates on inputs pins and effects such as clock gating. Furthermore, the prior art does not have a simple way of transposing the reliability models derived from one specifications to the other. This forces a complete reliability characterization of library at new conditions [JCS16]. Indeed, if the reliability condition changes towards the later end of the design cycle (referring back to Fig. 1.4), existing capabilities lack in providing the designers with a quick answer.

- Topological Considerations: The prior art makes a simplifying assumption of treating the entire system as a chain, thus resorting to the weakest link approximation. It should be however noted that in circuits, variety of topologies occur, and often there is redundancy, which implies that the failure of the first component does not imply circuit failure. Additionally, for on-chip interconnects, the EM failure is context-dependent, i.e., in some cases, even small changes in resistance may cause performance failures in the circuit and vice versa for others. For example, in clock-meshes

or in power grids, a large failure may be tolerated due to the inherent resilience in the circuit, where the failure of one wire may be compensated by current flow through other paths [JSC15,MS13]. Such topological considerations are valid for both: signal as well as power network and must be part of the EM verification method.

• Variability Handling: Interconnect currents comprise of switching and leakage, both of which are prone to statistical variations. In fact, with the advent of dark silicon, in our experience of industry chips, and as also noted by others, leakage can contribute up to 60% to the total power network current [MFT<sup>+</sup>08]. Further, such statistical process variations not only impact the current density, but also in the interconnect dimensions and the EM kinetics themselves. To our knowledge, such variations are not comprehensively addressed in prior art.

#### 1.4 Thesis Objectives

In the previous section, we claim that chip designers use simple, deterministic and bounding approaches for current estimation as well as threshold computation, which leads to entitlement loss in modern technologies. The thesis aims to reduce such entitlement loss by capturing the essence of physics-based models into the chip design. The thesis project aims at accomplishing the following objectives:

- Algorithms and Methodology for Logic-IP internal Electromigration Management

- \* In order to overcome the limitations of prior art on resistive load modeling, we present a unique and decoupled approach in this work. Our method additionally incorporates the impact of voltage-dependent pin capacitance on EM.

- \* Our model provides an on-the-fly retargeting capability for reliability constraints by allowing arbitrary specifications (of lifetimes, temperatures, voltages and failure rates), as well as interoperability of the IPs across foundries.

- Statistical Variations and Electromigration Verification

- \* Using detailed multivariate Hermite polynomial chaos, we model the impact of **non-Gaussian global process variations** on current density and EM kinetics.

- \* As a practical application in present industrial framework, we present a direct usage of above global variations model in determining the current flow under various workloads.

- \* Incorporate the impact of **local process variations** on EM. Our results demonstrate that the wires on lower metal layers are highly susceptible to local variations arising from transistor leakage.

- Topologically Aware Stochastic Methodologies for Accurate EM Assessment in Clock and Power Grids

- \* With specific application on clock grids, we present algorithms for EM assessment allowing us to incorporate and quantify the benefit from system redundancies. Taking the skew metric of clock-grid as a failure criterion, we demonstrate that unless such incorporations are done, chip lifetimes are underestimated by over 2x.

- \* Above bridge between component and system reliability is further extended through an extreme order statistics based approach, wherein, we demonstrate that system failures can be approximated reasonably by an asymptotic k-th component failure model, otherwise requiring costly Monte Carlo simulations. Using such approach, we can efficiently predict a system-criterion based time to failure (TTF) within existing EDA frameworks based on component level verification.

| Domain                                                     |                                                                                      | Prior Art                                                                                                                              | This Work                                                                                                         |

|------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Standard Cell EM<br>Analysis                               | Cell-internal current estimation under arbitrary switching rates                     | Restricted to simple cells [Dod15, US14]. Burd et al. showcased complex circuit tracing for current consumption [BAK <sup>+</sup> 13]. | Addressed through arc based current computations and demonstrated SPICE-like accuracy with significant speedup.   |

|                                                            | Incorporating parasitic wire loading and voltage dependent pin cap                   | NA: leads to significant pessimism [JJ12]                                                                                              |                                                                                                                   |

|                                                            | Retargetability under arbitrary reliability constraints                              | NA: prior art leads to<br>expensive recharacteriza-<br>tion under new reliability<br>constraints [BB13]                                | speedup.                                                                                                          |

| Clock Distribution<br>Network (Signal)<br>Electromigration | Incorporating topologi-<br>cal and contextual de-<br>pendencies                      | NA: no prior study high-<br>lighting how redundancy<br>impacts clock network<br>EM                                                     | Addressed and demonstrated possibilities of upto 2x pessimism reduction.                                          |

| Power Distribution<br>Network<br>Electromigration          | Global/local statistical<br>variations into current<br>estimation and EM<br>kinetics | No direct studies;<br>some in SRAM con-<br>text [GMSN14] but<br>present Monte Carlo<br>framework                                       | Addressed through efficient polynomial chaos method and (> 30%) better EM lifetime.                               |

|                                                            | Fast topological assessment and impact of EM violations on system failure            | NA: Monte Carlo based<br>[MS13]                                                                                                        | Addressed through<br>unique application of<br>extreme asymptotic<br>order statistics in non<br>Monte Carlo manner |

Table 1.1: Overall thesis contribution areas and comparison with prior art.

#### 1.5 Organization

The document is organized as follows: in Chapter 2, we review the background and the primer material needed to build upon the theories around reliability and statistics. In Chapter 3, we address the logic-IP internal Electromigration

problem. Subsequently, in Chapter 4, we introduce the stochastic and topologically aware Electromigration methodology, followed by the detailed analysis of statistical variations and its impact on EM in Chapter 5. Later, we present the conclusions and scope for future work in Chapter 6.

## Chapter 2

## Background

In this chapter, we will review the basic background material, beginning with the relevant introduction of Electromigration followed by a quick recapture of the basic probability terms essential in understanding the stochastic reliability analysis. Subsequently, we review the Monte Carlo random sampling approach from an Electromigration point of view. Finally, we review briefly the clock grid structure and existing EM challenges in clock and power grids.

### 2.1 Electromigration basics

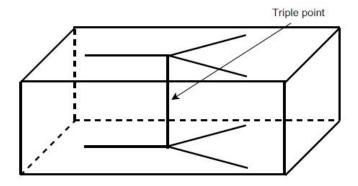

Electromigration is the mass transport of metal due to momentum transfer between electrons (driven by an electric field) and diffusing metal atoms. Such an event occurs when there is a flux divergence with regard to the movement of metal atoms, commonly at distortions-sites in the lattice, in the form of vacancies and/or grain boundaries [Lee13] which can be schematically represented by triple points (Fig. 2.1).

Figure 2.1: A typical triple point in a wire.

Flux divergence also arises when the flow of metal atoms into the region is

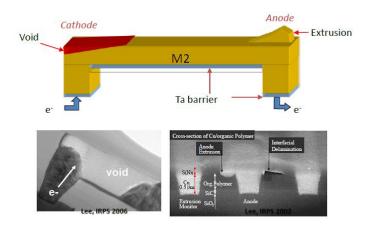

not equal to the outflow of atoms from the region [PJK10]. EM is associated with creation of either a void, or a hillock, as shown in Fig. 2.2 below.

Figure 2.2: Voiding and extrusion in Copper metal lines during Electromigration [Lee13].

A void is created due to depletion of atoms (when outflow from a region is greater than the flow into it) and leads to open-circuits or unacceptable resistance increase in a line. Whereas a hillock is created due to accumulation (when the flow into a region is greater than the outflow) of atoms and usually causes short-circuits between adjacent lines and inter-level conductors.

In this work, we assume for simplicity that all interconnect failures due to EM are caused by nucleation and/or growth of voids. Based on a very simple model, Black [Bla69] was the first to derive an expression for the time to failure of a metal line subjected to electromigration. He considered that the mean time to failure,  $t_{50}$ , is inversely proportional to the rate of mass transport,  $R_m$ ,

$$t_{50} \propto 1/R_m \tag{2.1}$$

and that the rate of mass transport is proportional to the momentum transfer between thermally activated ions and conducting electrons,

$$R_m \propto n_e \Delta P N_a \tag{2.2}$$

where  $n_e$  is the density of conducting electrons,  $\Delta P$  is the momentum transfer from the electrons to the metal atoms, and  $N_a$  is the density of thermally activated ions. Assuming that both the electron density as well as the momentum transfer are proportional to the current density, J,

$$n_e \propto J; \Delta P \propto J$$

(2.3)

and that the activated ions follow an Arrhenius law with the activation energy, Q,

$$N_a \propto exp(-Q/k_BT)$$

(2.4)

Consequently, the mean time to failure can be represented as:

$$t_{50} = A \frac{e^{Q/k_B T}}{J^n} \tag{2.5}$$

Here, J is the DC current density through the line, Q is the activation energy,  $k_B$  is Boltzmann's constant, n is the current exponent (typically between 1 to 2), and A is a fitting parameter. It was observed that not all experimental results followed the otherwise quadratic dependency of J. However, they could be fitted by allowing a variable current density exponent, n, which must again be experimentally determined.

#### 2.1.1 Alternative Electromigration Modeling Paradigms

At this point, it must be considered that EM failure occurs in two phases:

- Void nucleation: After a wire has been stressed, the depletion of atoms at the cathode creates a tensile stress. Once a critical stress threshold value has been crossed, the void nucleates.

- Void growth: After nucleation, further movement of metal atoms from the void results in void growth. This results in increased wire resistance due to the effectively reduced cross-section. If the void grows large enough, it may result in a break in the wire, resulting in either an open circuit or a vastly increased resistance, in cases where the current through the wire can flow through the higher-resistivity barrier layer of the copper.

Indeed, in the Black's equation (2.5), an exponent close to 1 indicates that the lifetime is dominated by the void growth mechanisms, *i.e.* the time for a void to grow and lead to failure represents the major portion of the lifetime [LK91], while a value close to 2 indicates that void nucleation is the dominant phase of the electromigration lifetime [KBT<sup>+</sup>93].

Eq. (2.5) has been used for lifetime estimation and extrapolation to operating conditions for 40 years now. However, in a recent publication Lloyd [Llo07] discussed the application of the modified equation, where nucleation and growth are explicitly accounted. If each of the processes is driven by the same driving force but exhibit different kinetics, the partition of the failure time is better represented as a joint function of driving forces as follows:

$$t_{50} = t_{nuc} + t_{growth} = \left(\frac{Ak_BT}{J} + \frac{B(T)}{J^2}\right)e^{\frac{Q}{k_BT}}$$

(2.6)

where A and B are constants that contain geometric information, such as the size of the void required for failure. Given any values for A and B, it follows that the relative contributions of nucleation and growth will vary as a function of the current density. At higher current densities the time to failure will proportionately be more growth than at lower current densities [Ori10].

#### Impact of Interconnect Topology

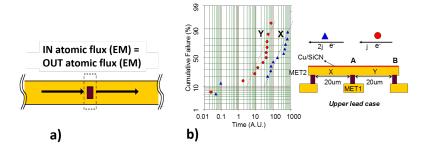

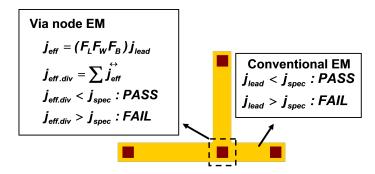

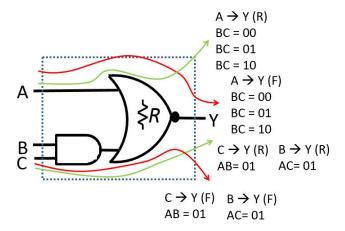

Additionally, it must be noted that fundamentally, void nucleation is driven by divergence of atomic flux which is typically highest at sites such as vias, contacts, or even points where the leads merge. Further, it has been reported in literature that even if the incoming atomic flux (signified by high current density) is high at such sites, the site itself may not fail due to it maintaining a low divergence; while a simple, individual-lead based Black's equation continues to predict failure for such a structure, as shown in Fig. 2.3a). This inefficiency has been recently revisited by various researchers resulting into evolution of alternative paradigms in EM checking [PJK10, ALTT04, GMSNL14].

A very clear demonstration of the topological effects can be seen through Fig. 2.3b). A two-lead system is shown here, where, the lead Y carries a current density of J, whereas the lead X a current density of 2J. The conventional wisdom assumes the two leads are isolated in terms of EM reliability. However, they are physically connected and their atomic flux indeed interacts. Thus, the actual divergence effect at the 'via node' A and 'via node' B is not purely determined by the local current density of the each lead X and Y, respectively. The lead EM interactions also affect the divergences at the via nodes. The lead Y, on the other hand, has a current flow of J but the current keeps flowing into X with a larger amount of 2J. The atomic flux from the lead Y does not piles up at the via node A but transfers into the lead X at faster rate due to the higher current density. This eventually increases the atomic depletion rate from the via node B and make the EM lifetime of the lead Y short. Indeed, while the conventional checks declare lead X to fail, it is lead Y which fails EM first, as also captured through the via-node vector method.

Fundamentally, such alternative methods rely on computing some form of atomic flux divergence at EM-probable sites and subsequently comparing them against set thresholds. One such method, as reported in [PJK10] is vector vianode based method, wherein the physical and directional interactions amongst various leads is incorporated to perform the reliability verification.

Notably, the fundamental inputs required to perform these effective divergence calculations still remain the individual current density in every single interconnect of the circuit, along with additional information like the circuit topology. For example, for the case considered in Fig. 2.4, all the individual

Figure 2.3: a) As the incoming and outgoing atomic flux are the same, the atomic flux divergence along the interconnect is zero, resulting in no EM damage b) Lead Y carries half current density of lead X but fails faster than lead X, contrary to the conventional EM expectation. The via-node vector EM method catches this using flux divergence [PJK10]

Figure 2.4: The via-node method compares the effective current density of a via node with the current density thresholds while the conventional method compares the current density. The via-nodes are most susceptible to the EM failures and the effective current density should be smaller than the thresholds. [PJK10].

lead currents are required to arrive at effective current density, along with additional factors like length, width and the interaction factors. The effective current density is in fact a product of these three factors to the individual current density, along with the vector sum. Notice that the conventional approach stop at checking individual current density against the threshold, while approaches such as these compute the effective current density, or divergence, and then compare it against the threshold. In summary, methods like these effectively capture the underlying physical phenomenon while still remaining in the realm of traditional Black's equation based verification framework.

#### 2.1.2 Electromigration under Bipolar (AC) Currents

It must be noted that a majority of wires in the circuits carry non-DC currents, for example, the output segment of a switching inverter circuit. While a sim-

ple summation to get mathematical average current of the waveform results in close to zero estimate, it has been demonstrated that such wires do fail EM, albeit with a much higher EM lifetime [TMHM93]. Therefore, adjustments are required to (2.5). A standard approach is to compute an effective-EM current, which is a constant current value, derived from the line current waveform that gives the same lifetime for that line under the influence of EM. Such an effective current can be computed based on some assumed periodic current waveform. Additionally, it has been empirically noted that EM damage recovers with the reversal in the current-flow direction [TCH93,Lee12]. Such recovery is accounted by adjusting the current calculation in following manner:

$$J = J_{avg}^+ - \kappa J_{avg}^- \tag{2.7}$$

Here,  $J_{avg}^+$  and  $J_{avg}^-$  indicate the average current density during current conduction in the positive and negative directions, respectively and  $\kappa$  is an empirically derived recovery factor (typically between 0.5-0.8). It has also been noted that the recovery phenomenon exhibits frequency dependence [TCH93], thereby meaning that wires with higher frequency tend to recover more than the lower one. However, this is still a subject of ongoing research [SHT15, HSK+16, DFN06] and in our work, we will treat all the wires with uniform recovery factor, which is the present industry practice.

## 2.1.3 Accelerated Electromigration Under Wire Joule Heating

Finally, a collateral event to Electromigration is that of Joule heating, which is related to the increase in wire temperature due to the constant current flow [Hun97]. In our context, we can make a simplifying assumption that the heat flows only from the metal lead to the silicon substrate. The silicon substrate, in turn, has a maximum allowed junction reference temperature  $(T_{ref})$ .  $T_{ref}$  can be achieved during circuit design by ensuring that the package thermal impedance is able to dissipate the total power dissipation.

Using the steady state for quasi-one-dimensional (1-D) heat transport, we get:

$$J_{RMS}^{2} = \frac{(T_{m} - T_{ref})K_{ox}w_{eff}}{t_{ox}t_{m}w_{m}\rho_{m}(T_{m})}$$

(2.8)

where,  $J_{RMS}$  is the RMS current density,  $T_m$  is the mean metal wire temperature,  $T_{ref}$  is the maximum allowed junction reference temperature in the silicon (for example 100 C),  $K_{ox}$  is the underlying oxide thermal conductivity,  $t_{ox}$  is the underlying oxide thickness,  $t_m$  is the metal thickness,  $w_m$  is the metal width,  $\rho_m$  is the temperature dependent metal resistivity, and  $w_{eff}$  is the effective thermal width. Above equation can be further simplified as follows, which relates

the increase in temperature ( $\Delta T$ ) over large scales of time, to RMS current in following manner, where c is a constant:

$$\Delta T = cJ_{RMS}^2 \tag{2.9}$$

Notice that above relation suggests that the wire temperature is a function of the RMS current, while on the other hand, EM reliability is a function of the average current, also accelerated by the wire temperature. In other words:

$$t_f \propto \frac{e^{Q/k_B T_m(J_{RMS})}}{J} \tag{2.10}$$

Pioneering work by Hunter [Hun97] combined the two effects of average EM fails and RMS-induced Joule heating in a self-consistent manner through the concept of duty cycles, making it possible to simultaneously check both conditions. If we define the effective duty cycle, r for a wire as the squared ratio of the average and the RMS current, we get:

$$r = \frac{J(T_m)^2}{J_{RMS}(T_m)^2} = J_{REF}^2 \left(\frac{e^{Q/k_B T_m}}{e^{Q/k_B T_{ref}}}\right) \frac{t_{ox} t_m w_m \rho_m(T_m)}{(T_m - T_{ref}) K_{ox} w_{eff}}$$

(2.11)

Since r is the squared ratio of the average and RMS currents, an unlimited number of current waveforms can have a given duty cycle. However, for a given r, there is only combination of RMS and AVG current which meets the Joule heating  $(\Delta T)$  and the EM reliability together. Thus, Hunter's method then simplifies to calculating the duty cycle for any given wire and looking up the allowed (AVG, or, RMS) current density for that particular r.

#### 2.1.4 Present Industry Approach

While above formulation (2.6) more suitably models the physics, it must be mentioned that industrially, Black's equation is still the workhorse model for EM verification [TSM16,GF16,ICF14]. As far as interconnect topologies are considered, formulations like via-node [PJK10] crisply break down the problem in current-computation and divergence calculations. Consequently, for this work, we a) keep our focus on Black's equation (2.5), b) restrict to topology-independent reliability verification and c) use a uniform recovery factor for all wires. All of above assumptions make us very relevant to the present approach in industrial EM verification frameworks from EDA vendors like Cadence, Synopsys and Ansys [EDI15, syn16, RED15], adopted all across the semiconductor industry and recommended by the semiconductor fabrication houses [TSM16, GF16, ICF14], thereby making our work directly applicable with minimal flow changes. Nevertheless, as we will show in later chapters, our formulations are flexible and could be extended to incorporate alternative paradigms of EM checking and to

interconnects with complex topologies.

#### 2.2 EM Reliability Mathematics

A failure-event for a wire is defined as the event when the line-resistance increases by 10% (or some such number). The TTF of a line (from (2.5)) is in fact, subject to variations. Indeed, an experiment pertaining a set of wires, made of the same material, using the same manufacturing process and with identical dimensions, stressed with the same current density J at a temperature  $T_m$  for time  $t_0$  will have a distribution of TTF. In other words, if we pick any single wire from the set, the only thing we know is the frequency distribution of the TTFs obtained from the experiment. To deal (rigorously) with such scenarios, we will be modeling the TTF of the lines using random variables.

#### 2.2.1 TTF Distribution: Lognormal

The type of distribution function used to characterize the lifetimes arising from a wide range of failure mechanisms (including EM), can be established theoretically or empirically. There have been various proposals on the model, with maximum agreement around the usage of log-normal model and will be used throughout this work.

Indeed, the initial failure rate, f(t), of each component is found to be log-normal, as represented by following relation:

$$f(t) = \frac{1}{t\sigma\sqrt{2\pi}}e^{\frac{-1}{2}\frac{\log(t) - \log(t_{50})}{\sigma}}$$

(2.12)

However, rather than the failure rate, it is the cumulative failure fraction fail fraction (FF) which is of higher importance. Indeed, FF follows a lognormal dependency on the time to failure ( $t_f$ , also known as stress time). The lognormal parameter (z), relates to the time-to-failure as follows, where  $\sigma$  is the standard deviation of the distribution, which is process-dependent:

$$z = \frac{1}{\sigma} \log \frac{t_f}{t_{50}} \tag{2.13}$$